HERIOT-WATT UNIVERSITY - POLYTECHNIC UNIVERSITY OF CARTAGENA

# Diseño a 2.45GHz de un Amplificador de Potencia GaN HEMT de Clase A (Resumen en Español)

PROYECTO FINAL DE CARRERA

**Autor: Pascual David Hilario Re**

Supervisor: José Luis Gómez Tornero Segundo supervisor: George Goussetis

Cartagena, Octubre 2015

| Autor              | Pascual David Hilario Re                                            |

|--------------------|---------------------------------------------------------------------|

| Email del autor    | pascual.hilario@gmail.com                                           |

| Director           | José Luis Gómez Tornero                                             |

| Email del director | josel.gomez@upct.es                                                 |

| Co-director        | George Goussetis                                                    |

| Título             | Diseño a 2.45GHz de un amplificador de potencia GaN HEMT de clase A |

#### Resumen

Hoy en día, la amplificación de estado sólido está dominada por el uso de transistores de tres terminales. Usando un pequeño voltaje aplicado en la entrada del dispositivo, uno puede controlar, de manera eficiente, una gran cantidad de corriente en el terminal de salida cuando el terminal común está conectado a tierra. Este es el origen del nombre transistor, que es la union de las palabras inglesas *transfer* y *resistor*.

Gracias a los transistors, la amplificación existe y este proyecto está enfocado en el proceso de diseño que un ingeniero debe seguir para llevarlo a cabo, desde las primeras simulaciones hasta su testeo en el laboratorio.

| Grado            | Ingeniería de Telecomunicación                        |  |  |

|------------------|-------------------------------------------------------|--|--|

| Departamento     | Tecnologías de la Información y las<br>Comunicaciones |  |  |

| Fecha de entrega | Octubre 2015                                          |  |  |

# **Índice de Contenidos**

| 1. | Intro | oducción                                                                | 1  |

|----|-------|-------------------------------------------------------------------------|----|

|    | 1.1.  | Transistor amplificador                                                 | 1  |

|    | 1.2.  | Beneficios de los Transistores-Amplificadores                           | 2  |

|    | 1.3.  | Objetivos                                                               | 3  |

|    | 1.4.  | Trasfondo teórico                                                       | 3  |

| 2. | Prod  | ceso de diseño de un Amplificador de Potencia                           | 5  |

|    | 2.1.  | Elección del transistor de microondas                                   | 5  |

|    | 2.2.  | Caracterización del transistor                                          | 5  |

|    | 2.3.  | Área de Operación Segura, punto de reposo (Q) y Línea de Carga Dinámica | 6  |

|    | 2.4.  | Análisis de estabilidad                                                 | 9  |

|    | 2.5.  | Simulación Load-Pull                                                    | 10 |

|    | 2.6.  | Redes de alimentación                                                   | 12 |

|    | 2.7.  | Diseño real                                                             | 16 |

| 3. | Proc  | ceso de Fabricación y Testeo                                            | 23 |

|    | 3.1.  | Elección del disipador de calor                                         | 23 |

|    | 3.2.  | Conexión a tierra del transistor                                        | 24 |

|    | 3.3.  | Testeo                                                                  | 25 |

|    | 3.4.  | Resultados                                                              | 27 |

|    | 3.5.  | Problema térmico                                                        | 27 |

|    | 3.6.  | Conclusiones                                                            | 28 |

|    | 3.7.  | Líneas futuras                                                          | 28 |

### 1. Introducción

#### 1.1. Transistor amplificador

Hoy en día, la amplificación de estado sólido está dominada por el uso de transistores de tres terminales. Usando un pequeño voltaje aplicado en la entrada del dispositivo, uno puede controlar, de manera eficiente, una gran cantidad de corriente en el terminal de salida cuando el terminal común está conectado a tierra. Este es el origen del nombre transistor, que es la unión de las palabras inglesas transfer y resistor.

Los transistores de estado sólido se pueden agrupar en dos categorías: dispositivos unipolares y bipolares. La amplificación de señales es una función fundamental en todos los sistemas de RF y microondas.

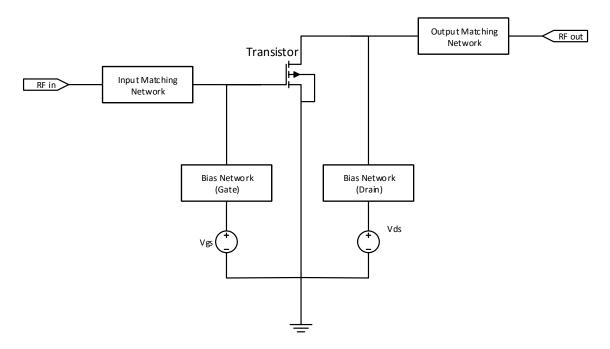

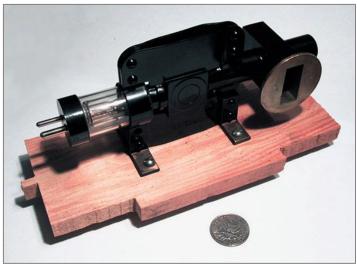

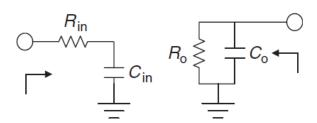

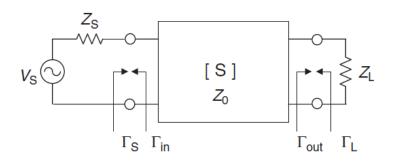

Cuando la fuerza de una señal débil es incrementada por un dispositivo usando una alimentación de corriente continua (DC), dicho dispositivo con su circuitería tanto de adaptación como de alimentación es conocido como un amplificador. Aquí, la potencia DC de la alimentación se convierte en potencia RF para mejorar la potencia de la señal de entrada. Si el dispositivo es un transistor, la señal aplicada a la entrada (puerta/base) y la señal amplificada aparece en la salida (drenador/colector) y el terminal común (fuente/emisor) va generalmente a tierra. Las redes de adaptación ayudan excitando el dispositivo y recolectando la señal de salida de una manera más eficiente. La Figura 1.1 nos muestra una representación esquemática de un amplificador (transistor) de una sola etapa. Los constituyentes son un transistor, redes de adaptación tanto en la entrada como en la salida, circuitería de alimentación y conexiones RF de entrada y salida.

Figura 1.1 – Esquemático de un transistor amplificador.

El diseño de amplificadores requiere esencialmente modelos de dispositivos / parámetros S, herramientas CAD, redes de adaptación y alimentación, y tecnología de fabricación. Amplificadores de RF y microondas tienen las siguientes características:

- Banda limitada de respuesta RF

- Menos del 100% de eficiencia de conversión de DC a RF

- No-linealidades que generan productos de intermodulación entre multiples señales

- Acoplo RF y no respuesta de DC

- Amplitud dependiente de la potencia y diferencia de fase entre la entrada y la salida

- Ganancia dependiente de la temperature, mayor ganancia a bajas frecuencias y viceversa

#### 1.2. Beneficios de los Transistores-Amplificadores

Las principales ventajas de los amplificadores de transistores frente a los amplificadores de tubo son:

- Menor tamaño

- Menor peso

- Mayor fiabilidad

- Alto nivel de capacidad de integración

- Alto volumen y alto rendimiento de capacidad de producción

- Mayor flexibilidad en el diseño

- Menores voltajes de alimentación

- Mantenimiento requerido reducido

- Diversidad de aplicaciones ilimitada

- Tienen mucha más vida operativa (en el orden de millones de horas)

- Requieren mucho menos tiempo de calentamiento

Además, los amplificadores de estado sólido no requieren ajustes en la alimentación o en el circuito tal y como lo requieren los amplificadores de tubo en largos periodos de operación.

#### 1.3. Objetivos

Los principales objetivos y propósitos de este proyecto final son:

- Aprender el trasfondo teórico sobre el diseño de un amplificador de potencia.

- Realizar el diseño y simularlo a través de AWR (Microwave Office).

- Fabricar el prototipo final y testearlo en el laboratorio.

Las especificaciones de nuestro amplificador de potencia serán:

- Trabajar en la banda WiFi (2.45GHz) en una configuración de banda estrecha (100MHz).

- Al menos 14dB de ganancia a esa frecuencia.

#### 1.4. Trasfondo teórico

Toda la teoría básica relativa a este proyecto se encuentra en la versión inglesa de la memoria.

# 2. Proceso de diseño de un Amplificador de Potencia

#### 2.1. Elección del transistor de microondas

Un dispositivo idóneo que funcione como se pretende es muy esencial. Por ello, un estudio detallado de varios datasheets es imprescindible para no equivocarnos a la hora de elegir nuestro transistor.

Teniendo en cuenta nuestras especificaciones y ya que se han vuelto muy populares en los últimos años hemos decidido usar un GaN HEMT (Gallium Nitride High Electron Mobility Transistor). Los GaN HEMT ofrecen alta eficiencia, alta ganancia y gran ancho de banda haciéndolos ideales para amplificadores tanto lineales como comprimidos. Además de todo lo ya expuesto, otra de sus principales ventajas es el bajo consumo de energía.

Teniendo en cuenta todas estas ventajas, el transistor escogido finalmente es el CGH40010F de Cree Inc. El modelo de dicho transistor ha sido facilitado por la compañía a través de un portal web accesible mediante registro desde el cual nos descargaremos el modelo para su posterior uso en AWR.

#### 2.2. Caracterización del transistor

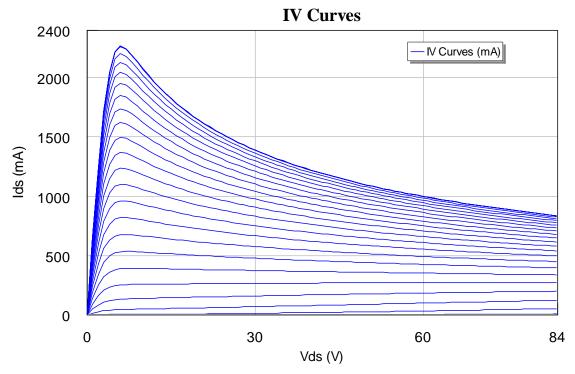

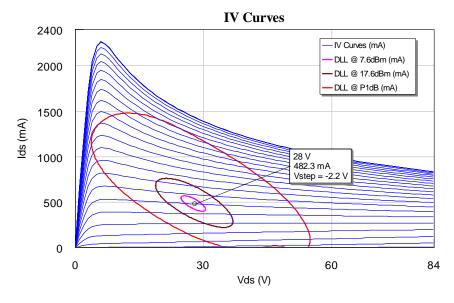

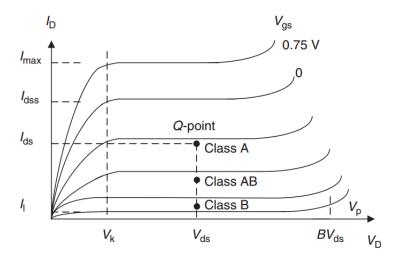

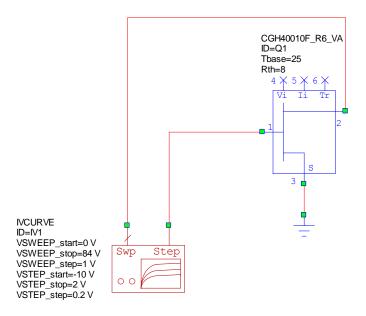

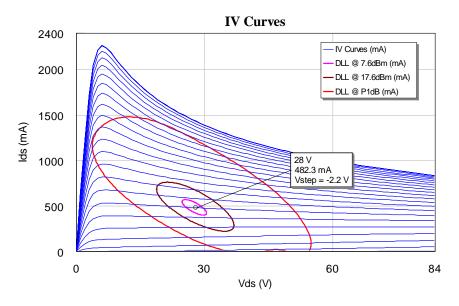

Una vez que el modelo es importado a AWR, un esquemático con el elemento IVCURVE es necesario para dibujar las curvas IV de nuestro transistor. Dichas curvas las podemos observar en la Figura 2.1.

Figura 2.1 - Curvas IV del CGH40010.

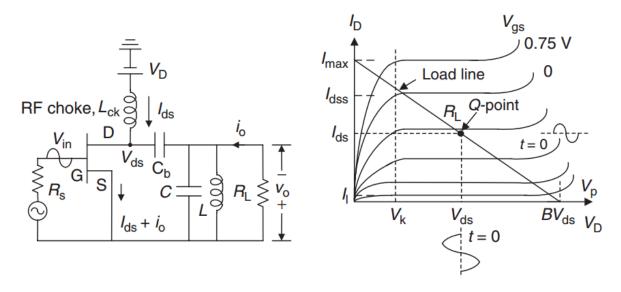

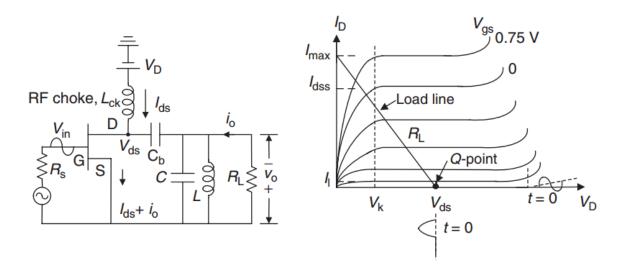

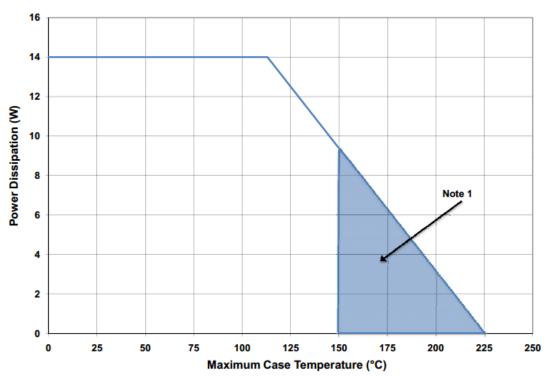

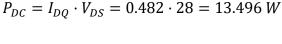

# 2.3. Área de Operación Segura, punto de reposo (Q) y Línea de Carga Dinámica

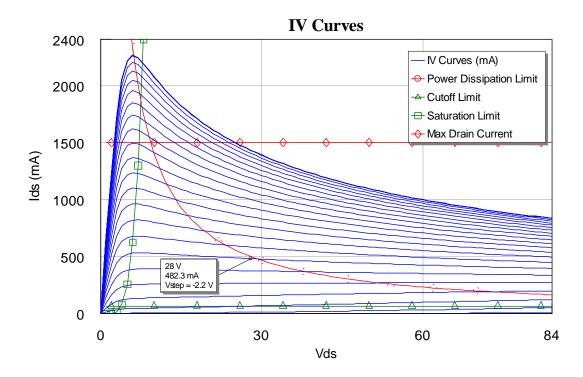

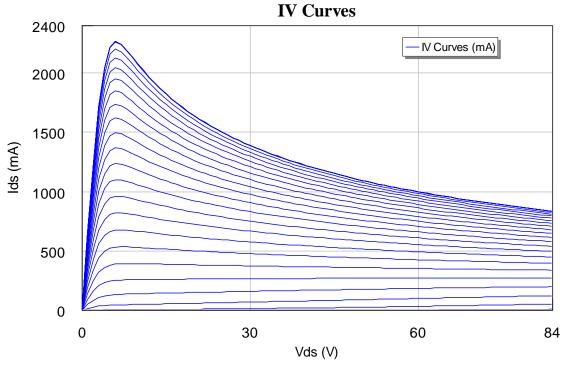

Ahora debemos fijar las condiciones de alimentación. Fijando los voltajes de alimentación de la puerta ( $V_{gs}$ ) y el drenador ( $V_{ds}$ ) determinaremos la posición de nuestro punto de reposo en la región activa de las curvas IV. Para definir el Área de Operación Segura, necesitamos marcar en la gráfica de curvas IV los límites que hacen que el transistor o no funcione correctamente o se rompa. Dichos límites son cinco: corte, saturación, máxima corriente de drenador, máximo voltaje de drenador y máxima disipación de potencia.

Los límites de corte y saturación se obtienen de manera orientativa sobre la propia gráfica. La máxima corriente de drenador la obtenemos del datasheet del transistor además de la máxima potencia disipada.

$$P_{diss} = P_{gate} + P_{drain} \approx P_{drain} = V_{ds} \cdot I_{ds}$$

$$P_{dissMax} = 14 \approx V_{ds} \cdot I_{ds}$$

$$I_{ds} \approx \frac{14}{V_{ds}}$$

Esta última ecuación representa la curva de la máxima potencia disipada, con ella seremos capaces de dibujarla sobre las curvas IV y así delimitar la región segura de la región de sobrecalentamiento.

Dado que trabajamos en Clase A hemos decidido tomar los siguientes valores de alimentación:

$$V_{gs} = -2.2 V$$

$$V_{ds} = 28 V$$

Figura 2.2 – Área de Operación Segura y Punto de Reposo.

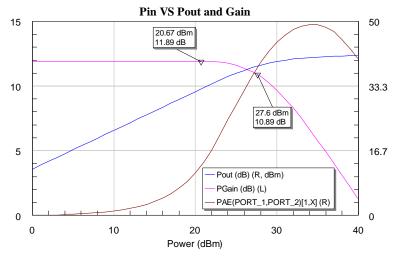

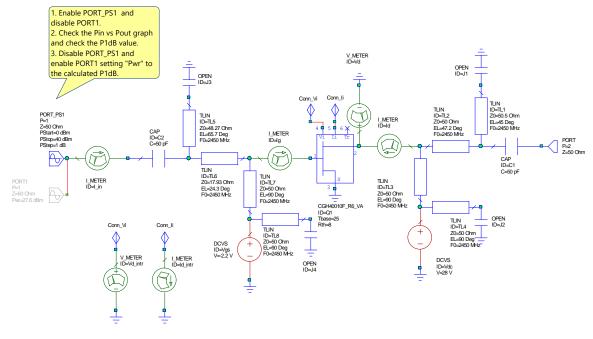

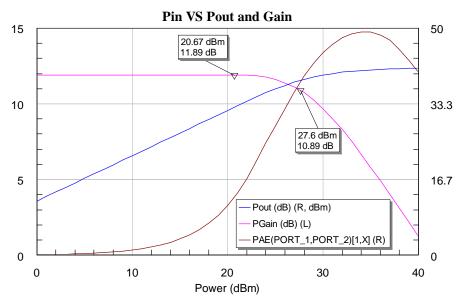

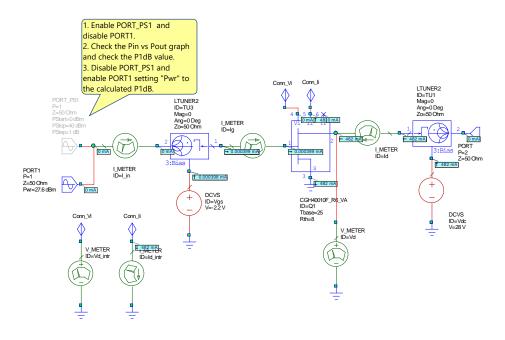

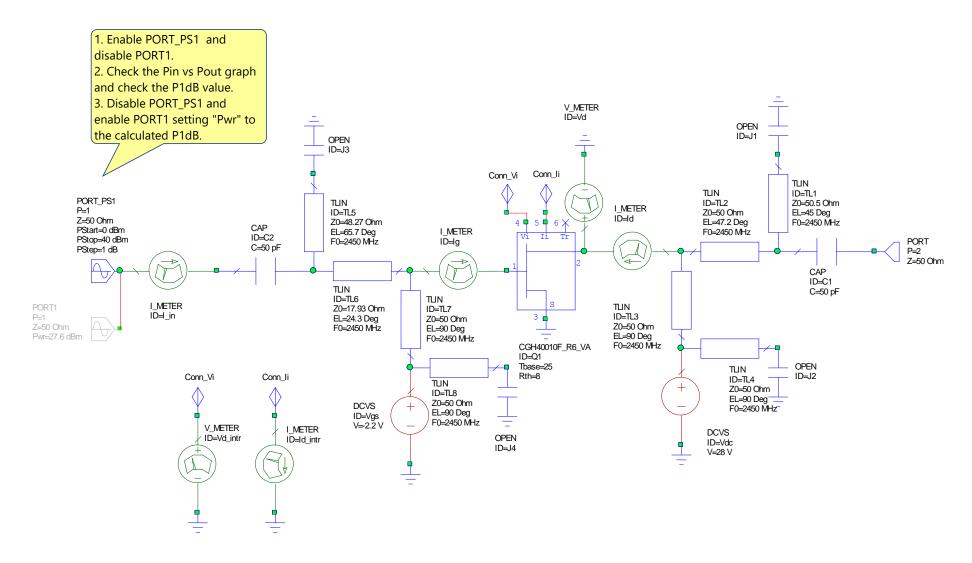

Ahora pasamos a obtener el  $P_{1dB}$  para así dibujar la línea dinámica de carga con dicha potencia a la entrada.

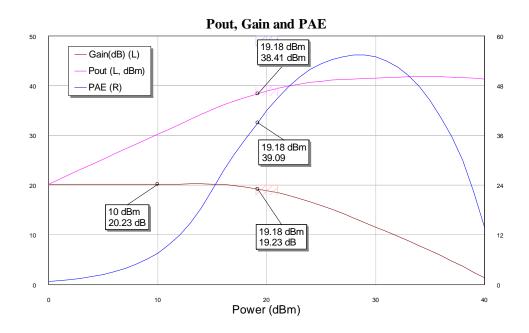

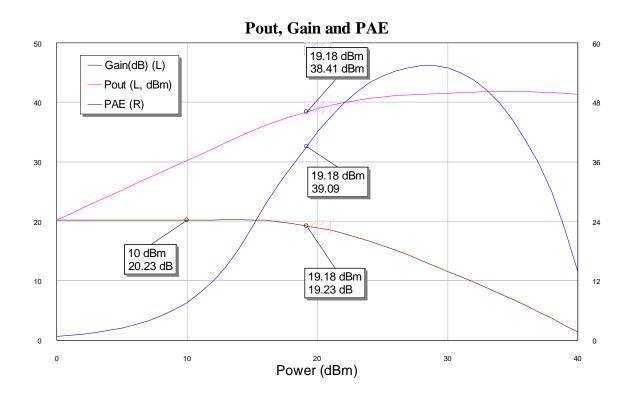

Como podemos observar en la Figura 2.3, vemos que dicho valor está en 27.6dBm, por tanto, será el que aplicaremos a la entrada tal y como hacemos en la Figura 2.4.

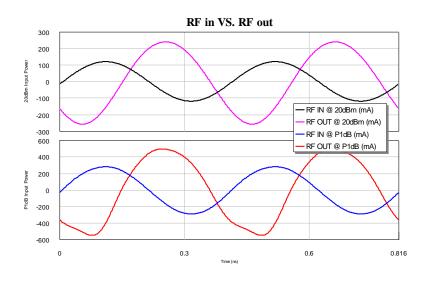

Varias potencias hemos aplicado. Los resultados en términos de líneas dinámicas de carga se pueden observar en la Figura 2.5.

Figura 2.3 – CGH40010 Pout, Ganancia y PAE.

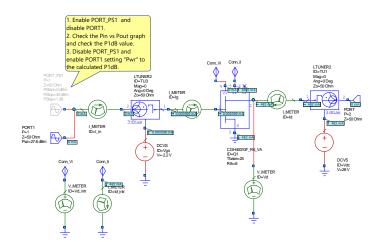

Figura 2.4 – Esquemático para testear, entre otras cosas, la ganancia, PAE y potencia de salida iniciales.

Figura 2.5 – Líneas dinámicas de carga para distintas potencias de entrada.

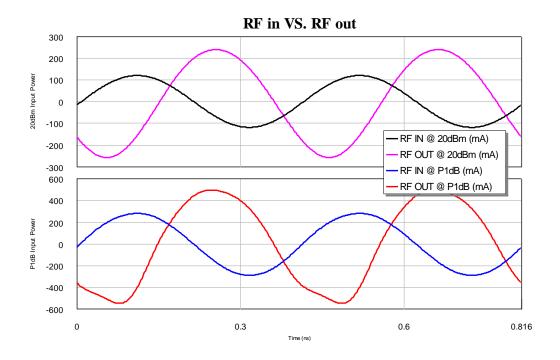

Aquí podemos observar una comparativa entre trabajar en región lineal (Figura 2.6 – arriba) y trabajar en región de saturación (Figura 2.6 – abajo) donde empiezan a aparecer nolinealidades.

Figure 2.6 – Current waveforms both in linear and saturation.

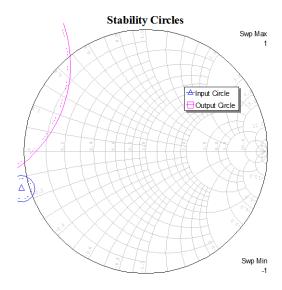

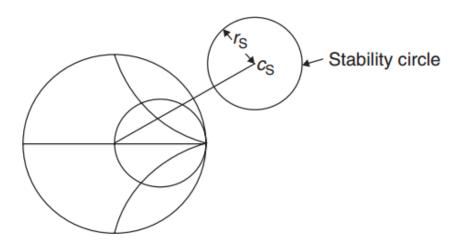

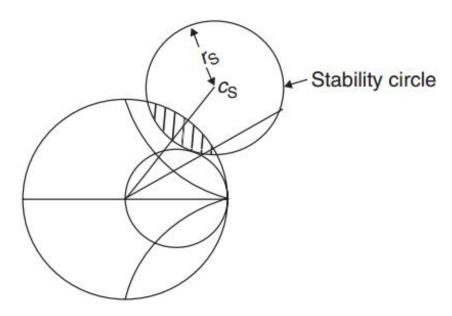

#### 2.4. Análisis de estabilidad

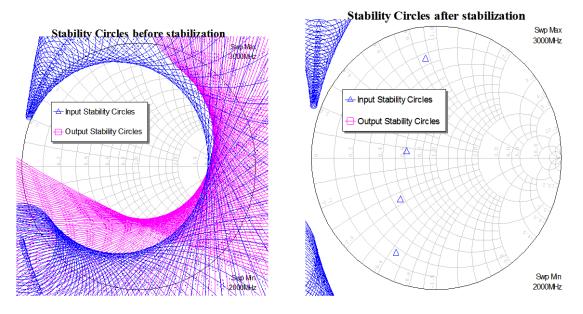

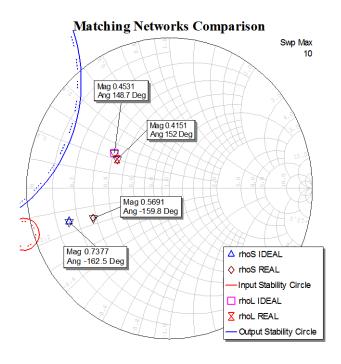

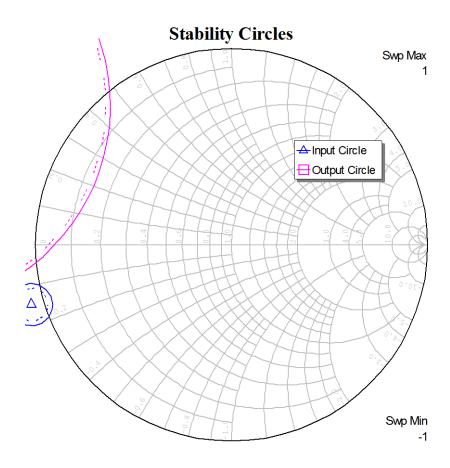

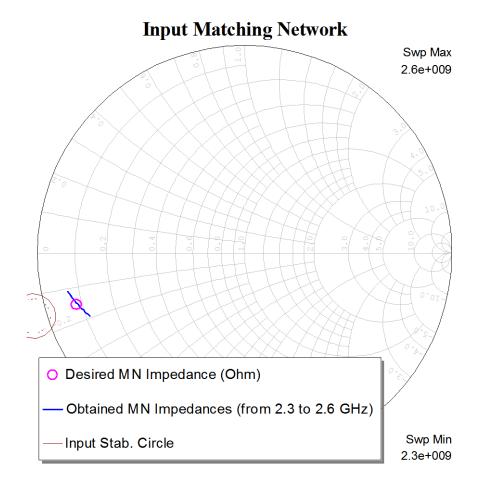

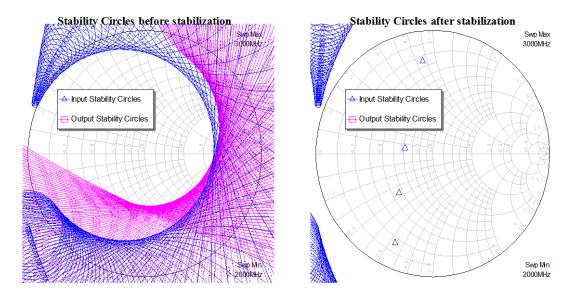

Realizar este estudio mediante AWR es muy sencillo. En *measurements* elegimos tanto *SCIR1*, para la estabilidad en la entrada, como *SCIR2*, para la estabilidad en la salida. Podemos ver el resultado en la Figura 2.7.

Las líneas discontinuas marcan la región del círculo que es inestable. En nuestro caso, las líneas discontinuas marcan que el interior de las circunferencias son las zonas inestables. Así pues, la intersección entre el interior dichas circunferencias y la carta de Smith serán las zonas que tendremos que evitar a la hora de diseñar tanto la red de entrada como la de salida.

Así que gracias a esta simple medida en AWR, podemos ahorrarnos todos los cálculos analíticos que supondría el llevarlo a cabo a mano.

Figura 2.7 – Círculos de estabilidad de entrada y salida a 2.45GHz.

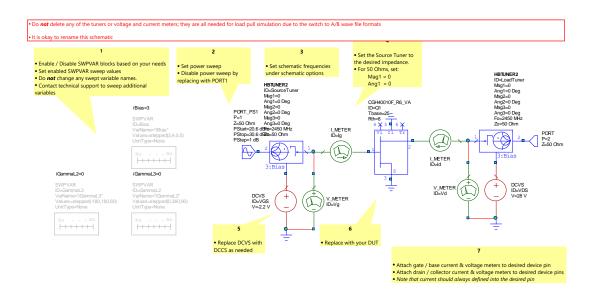

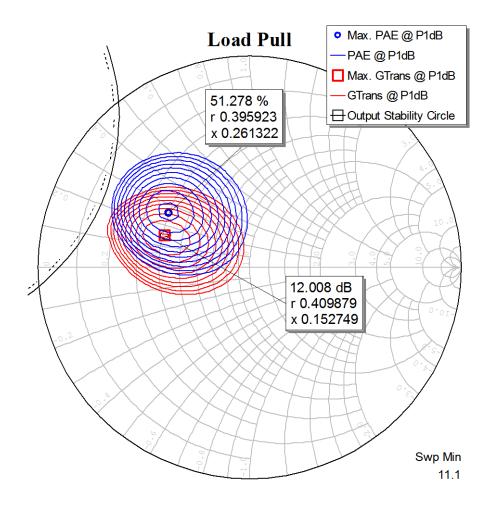

#### 2.5. Simulación Load-Pull

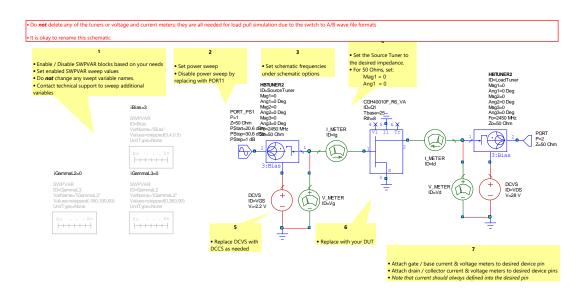

Este método básicamente consiste en utilizar un elemento *LTUNER2*, el cual hace un barrido de coeficientes de reflexión en la red de salida, evaluando para cada punto los valores de PAE, ganancia y potencia disponibles, entre otros, con tal de encontrar el valor óptimo. El valor de coeficiente de reflexión a la salida tiene que entrar en concordancia con el estudio de estabilidad llevado a cabo anteriormente, esto es, no elegir un punto que esté dentro de la región inestable.

Figura 2.8 – Plantilla de Load-Pull generada automáticamente por AWR.

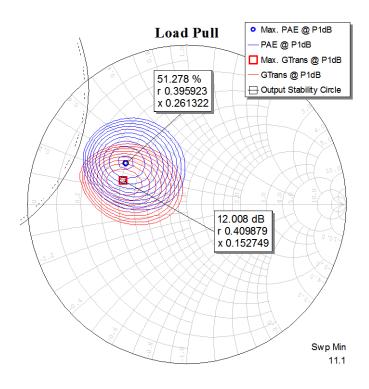

Figura 2.9 – Contornos de G<sub>Trans</sub> y PAE.

Como podemos observar en la Figura 2.9, tanto el máximo en PAE como el máximo en ganancia están muy cerca, lo que nos hace decidirnos por un punto en esa zona, ya que además se encuentra en la región estable. Este punto es

$$\Gamma_{out} = 0.44152 \angle 149.3904^{\circ}$$

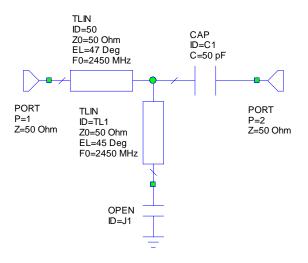

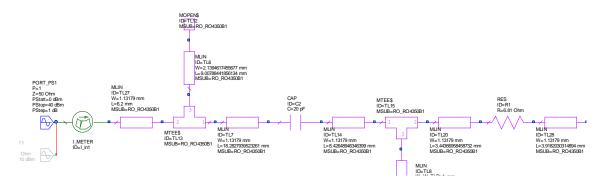

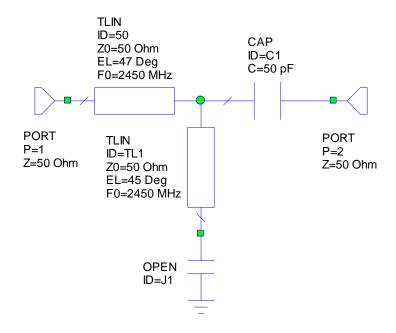

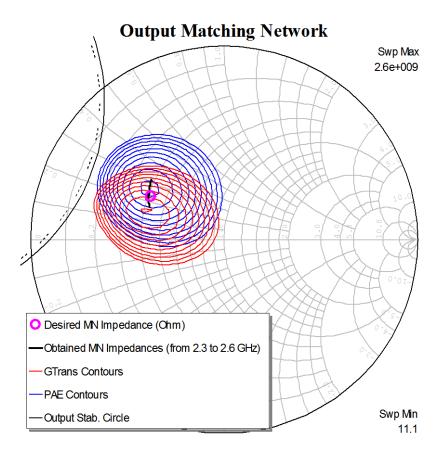

La red de adaptación de salida que nos proporciona dicho coeficiente de reflexión es la mostrada en la Figura 2.10.

Figure 2.10 – Red de adaptación a la salida.

La función del condensador *C1* es la de bloquear el paso de la DC así la alimentación va directamente al drenador y no se pierde por el puerto de salida.

Ahora, llevamos a cabo un análisis manual con el optimizador de AWR. Los resultados obtenidos concuerdan con lo que dice la teoría: la máxima transferencia de potencia se producirá cuando el coeficiente de reflexión de la carga sea igual al conjugado al coeficiente de reflexión que se ve hacia la puerta del transistor. Dicho valor es el siguiente

$$\Gamma_S = 0.85 \angle - 163^{\circ}$$

Este resultado no es exactamente el conjugado, ya que el conjugado estaba muy cerca de la zona de inestabilidad lo que nos hizo escoger un valor un poco más alejado de esa zona y más cercano al centro de la carta de Smith.

Figura 2.11 – Red de adaptación a la entrada.

#### 2.6. Redes de alimentación

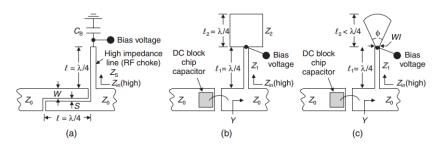

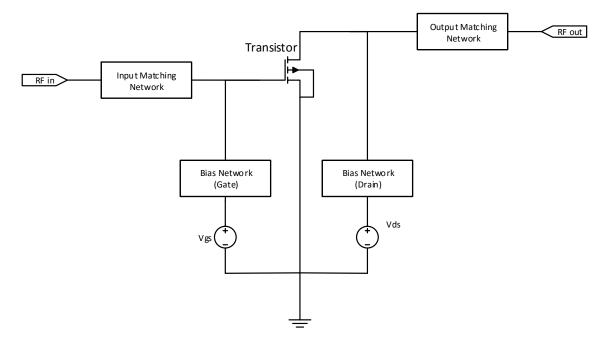

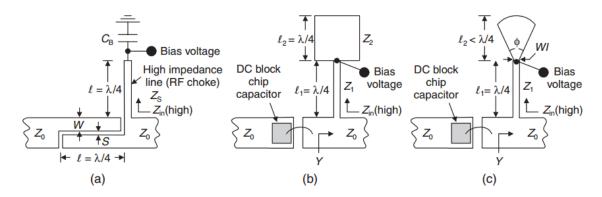

Figure 2.12 – Circuitos de alimentación de microondas simplificados: (a) bloqueo de DC por línea acoplada y transformador de  $\lambda/4$ , (b) bloqueo de DC con condensador MIM y dos transformadores  $\lambda/4$ , y (c) bloqueo de DC por condensador MIM y un transformador de  $\lambda/4$  en serie con un stub radial.

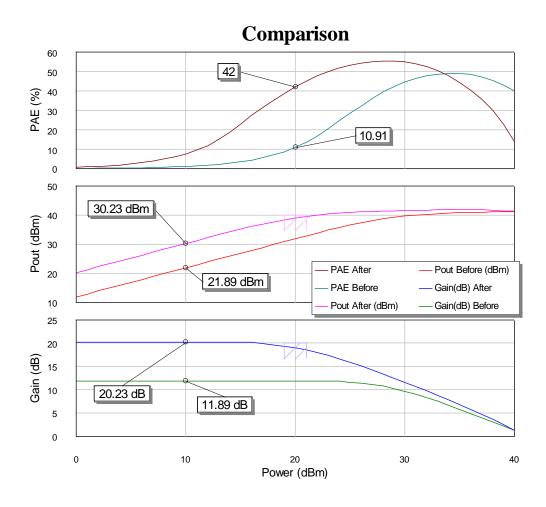

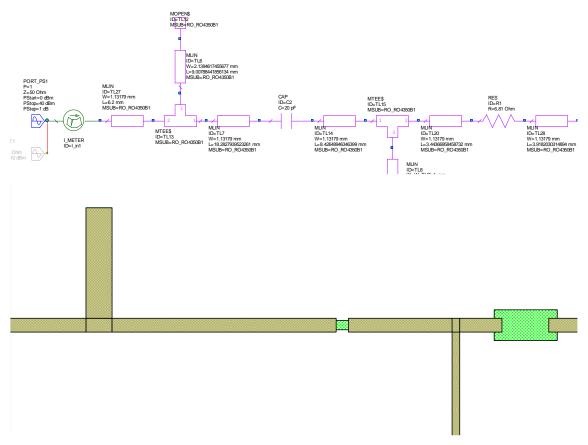

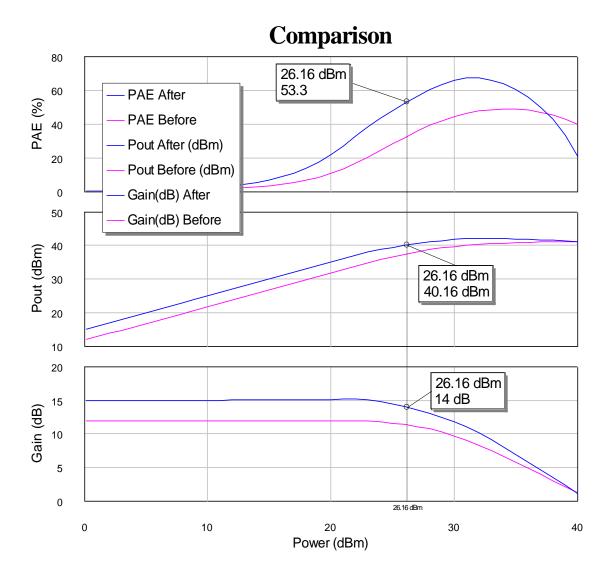

En el diseño sin pérdidas inicial (ideal) decidimos usar la segunda configuración mostrada en la Figura 2.12. El diseño final sin pérdidas se puede ver en la Figura 2.14 y los resultados de PAE, ganancia y potencia de salida se muestran en la Figura 2.13.

Figura 2.13 – Pout, ganancia y PAE obtenidos con el diseño ideal.

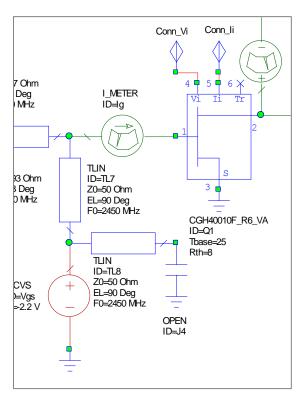

Figura 2.14 – Diseño final con líneas de transmisión ideales.

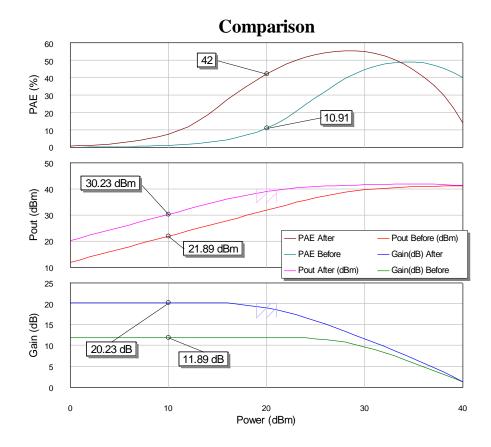

Figura 2.15 – Comparación entre el diseño realizado y el transistor sin ningún tipo de red de adaptación.

Tal y como podemos observar en la Figura 2.15, hemos mejorado el rendimiento de nuestro amplificador con esta configuración final.

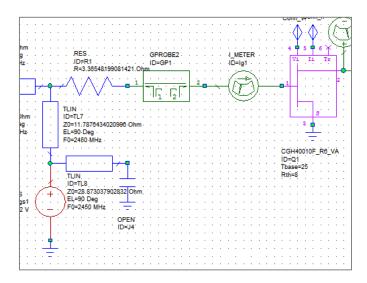

Ahora, el principal problema es que hemos obtenido unos parámetros S muy malos, además de poca estabilidad. Dicho problema se puede evitar añadiendo una resistencia a la puerta.

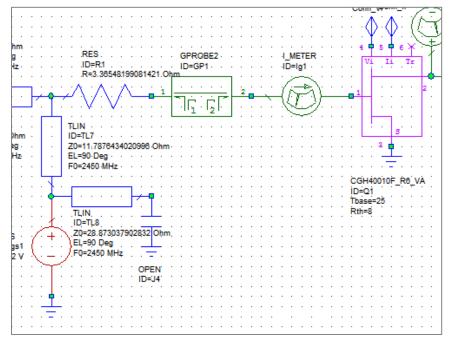

**Figura 2.16** – Resistencia añadida a la puerta para mejorar en estabilidad y en adaptación a  $f_0$ .

Figura 2.17 – Adaptación mejorada al colocar la resistencia en la puerta.

**Figura 2.18** – Círculos de estabilidad antes (izquierda) y después (derecha) de colocar la resistencia en la puerta del transistor. Se puede observar que conseguimos estabilidad incondicional entre 2 y 3 GHz.

#### 2.7. Diseño real

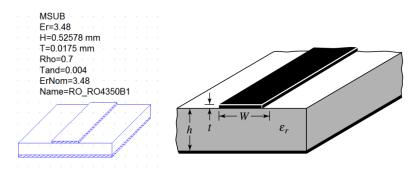

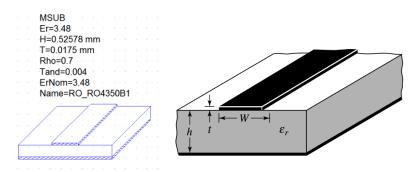

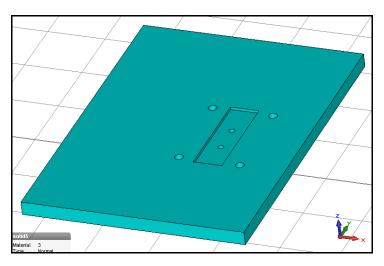

Al pasar a un diseño real (con pérdidas) debemos, primero, saber el sustrato que vamos a utilizar. El sustrato elegido ha sido el modelo RO4350B-LoPro de Rogers Corp. (20 micras de grosor). Nos decidimos por este grosor debido a que cuanto más fino sea el sustrato, mejor conductividad térmica tendremos.

Para tener en cuenta dicho sustrato en nuestras simulaciones, debemos incluir en nuestro esquemático el elemento *MSUB*, al cual deberemos darle los parámetros del sustrato que podemos encontrar en el datasheet del mismo.

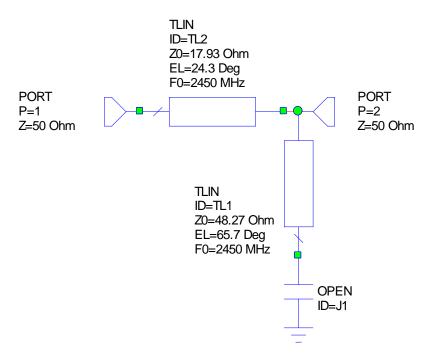

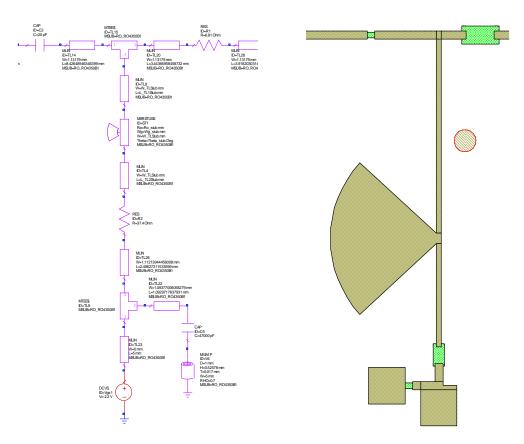

Figura 2.19 – Elemento MSUB (izquierda) y parámetros de la línea microstrip (derecha).

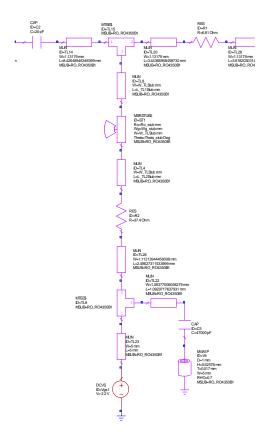

Una vez hecho esto, pasamos a reemplazar todas las líneas *TLIN* por líneas que simulan pérdidas, líneas reales, llamadas *MLIN*. Además, debido a la mala respuesta de la red de alimentación, decidimos cambiarla por la tercera configuración de la Figura 2.12, esto es, con stub radial en paralelo además de una línea de alta impedancia que conecta dicho stub radial con la red de adaptación de entrada. Con esta configuración mejoramos el ancho de banda además de que el stub radial hace mejor su función como inductor bloqueando el paso de RF. La red de alimentación la podemos observar en la Figura 2.20.

Figura 2.20 – Esquemático de la red de alimentación con pérdidas.

Aparte del stub radial bloqueador de RF, usamos una resistencia entre dicho bloqueador y la alimentación. Su propósito no es más que estabilizar las bajas frecuencias.

Fuera de nuestro ancho de banda habrán ciertas frecuencias que no verán altas impedancias a través de la red de alimentación por lo que es importante usar condensadores de desacoplo en paralelo con la fuente de alimentación. De esta manera, la RF que se cuele quedará cortocircuitada por este condensador.

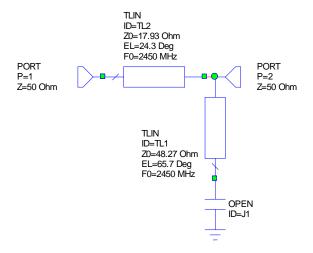

Figura 2.21 – Esquemático de la red de adaptación a la entrada con pérdidas.

Como podemos ver en la Figura 2.21 usamos como red de adaptación un stub acabado en abierto y algunas líneas de transmisión en serie con la misma anchura y, por lo tanto, impedancia (50  $\Omega$ ).

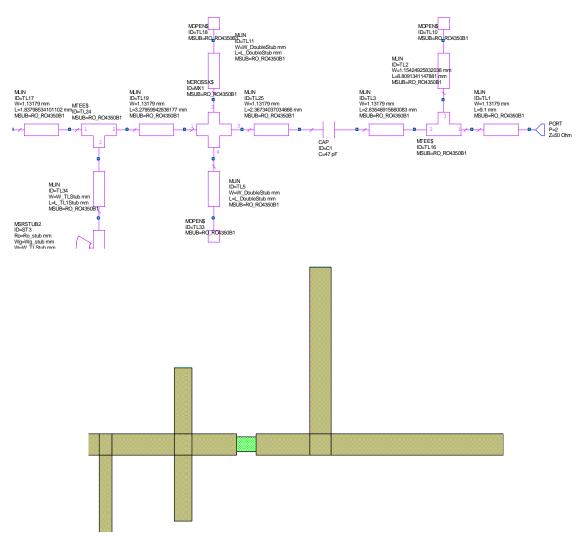

En la red de adaptación a la salida, como se puede observar en la Figura 2.22, usamos un doble stub acabado en abierto además de un solo stub acabado también en abierto. El condensador responsable de evitar la fuga de DC por el puerto de salida se ha colocado en el centro ya que durante el proceso de optimización nos dio mejores resultados en dicha posición. Dicho proceso de optimización se llevó a cabo teniendo en cuenta la obtención de la mejor adaptación, ganancia y estabilidad.

Figura 2.22 – Esquemático de la red de adaptación a la salida con pérdidas.

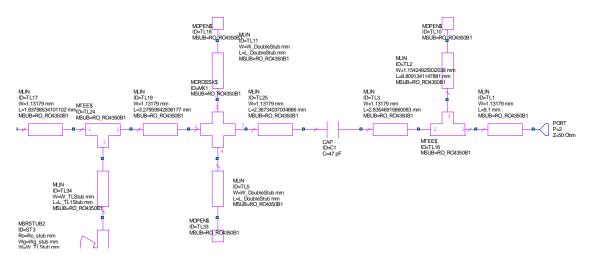

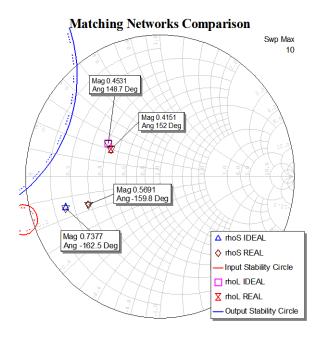

Figura 2.23 – Redes de adaptación reales (con pérdidas) Vs. Redes de adaptación ideales (sin pérdidas).

Para tener una idea de cuán diferentes son las redes de adaptación reales e ideales se ha realizado una comparativa de los coeficientes de reflexión asociados en la Figura 2.23. Se puede observar en dicha Figura que dichos coeficientes están bastante cercanos a lo que se buscaba idealmente.

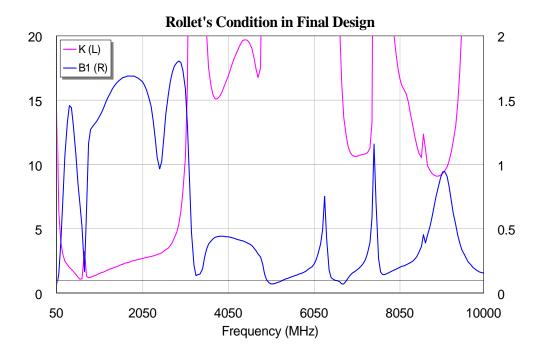

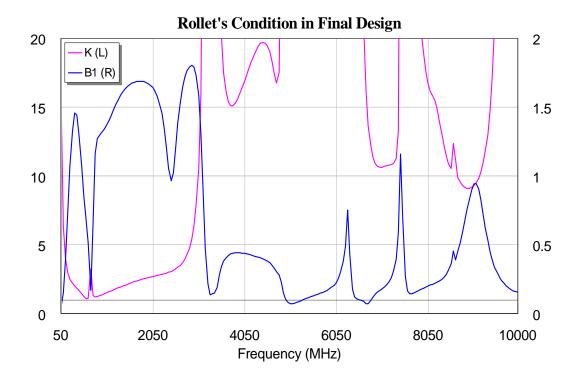

Figura 2.24 – Test final de estabilidad incondicional.

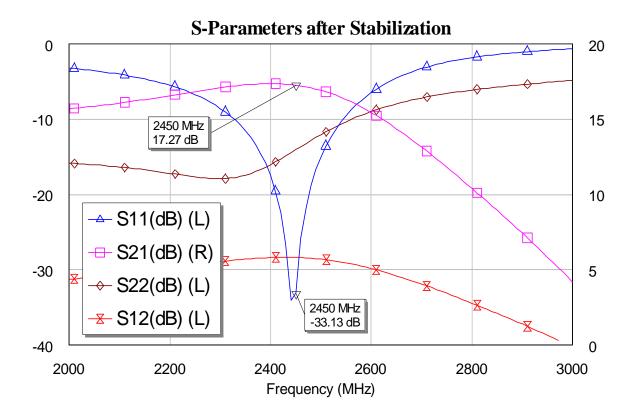

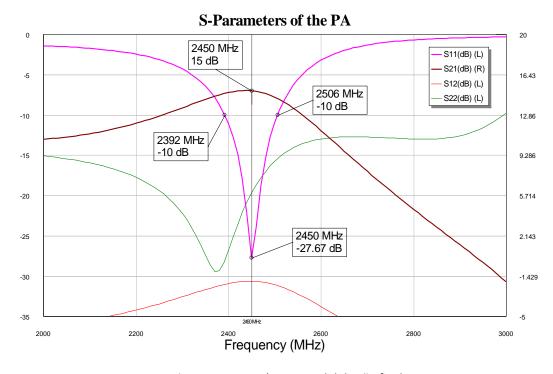

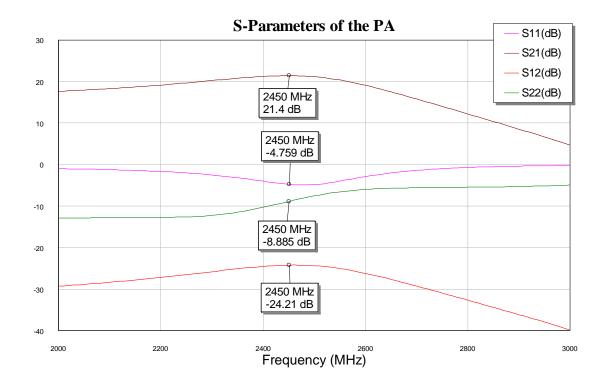

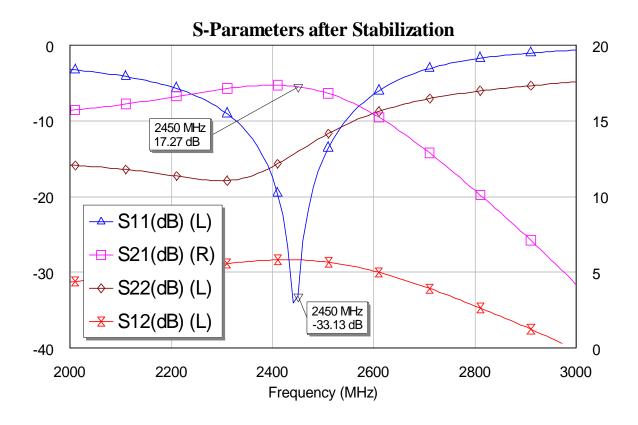

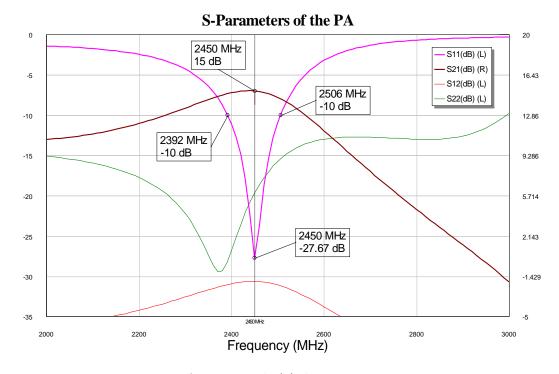

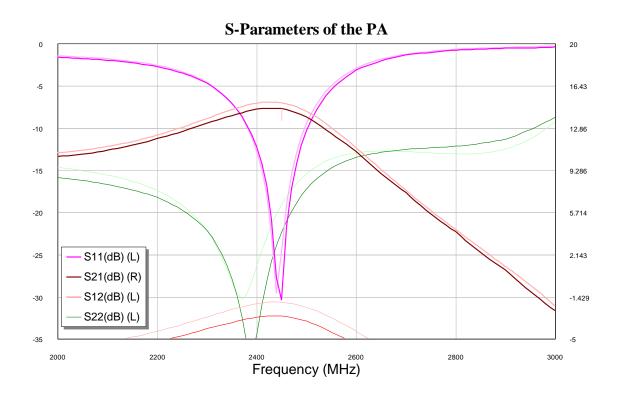

Figura 2.25 – Parámetros S del diseño final.

La estabilidad incondicional se ha comprobado en un amplio rango de frecuencias (entre 0.05 y 10GHz) con resultados muy positivos como se muestra en la Figura 2.24.

Además, los parámetros S, mostrados en la Figura 2.25, nos muestra que alcanzamos una ganancia de unos 15dB a la frecuencia de trabajo (2.45GHz) y alrededor de unos 100MHz de ancho de banda a -10dB.

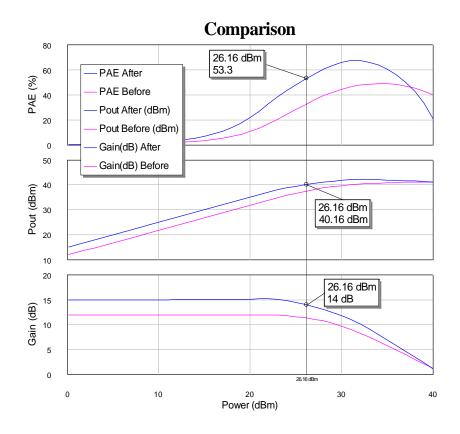

Finalmente, comparamos el rendimiento del transistor con el que proporciona el diseño realizado con pérdidas. Dicho diseño mejora al transistor unos 3dB, aproximadamente.

Figura 2.26 – Comparación final – Transistor Vs. Diseño final.

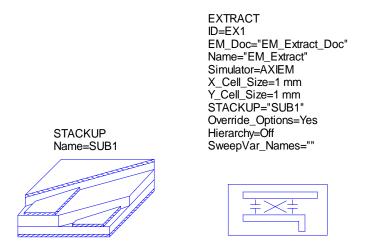

Antes de empezar a trabajar en el proceso de fabricación es importante hacer una simulación final teniendo en cuenta las pérdidas por acoplo y otros fenómenos provocados por la interacción de campos electromagnéticos. Debido a que el análisis llevado a cabo hasta ahora ha sido a nivel circuital, tenemos ahora que incorporar las interacciones de los campos y observar cómo afectan a nuestro diseño final.

La simulación que incorpora estas interacciones es bastante lenta ya que debe tener en cuenta muchas más cosas. Haciendo ahora una comparación sin tener y teniendo en cuenta la interacción de los campos podemos observar que no se manifiesta un cambio significativo.

Figura 2.27 – Comparación con y sin extracción electromagnética (EM Extraction).

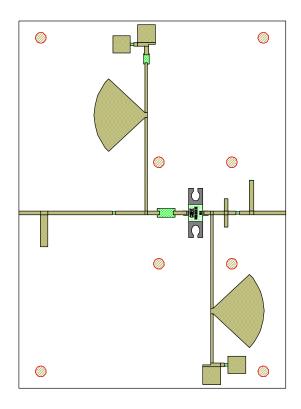

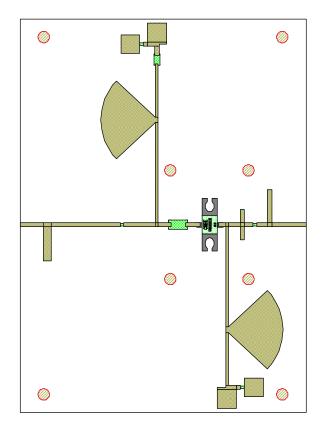

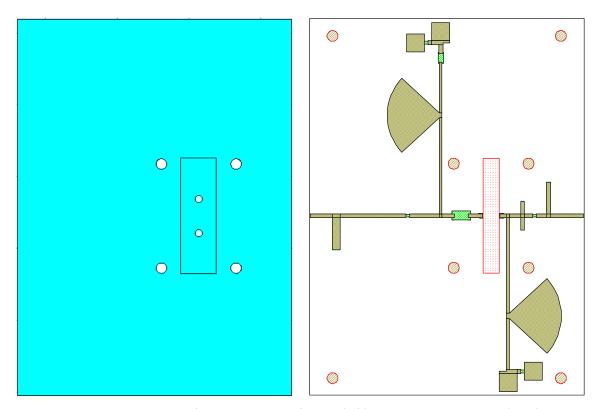

En la Figura 2.28 podemos observar el aspecto de nuestro diseño final en tecnología microstrip, listo para empezar el proceso de fabricación.

Figura 2.28 – Diseño final.

## 3. Proceso de Fabricación y Testeo

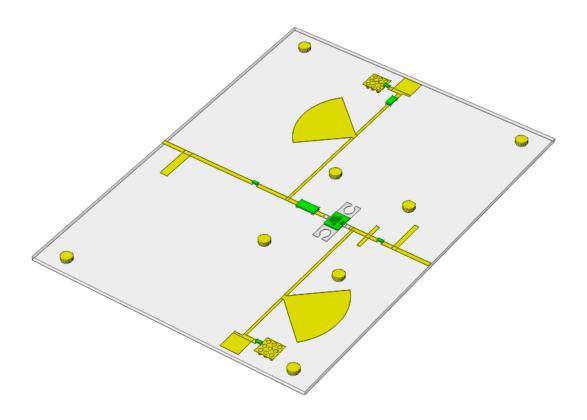

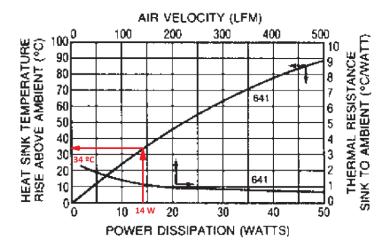

#### 3.1. Elección del disipador de calor

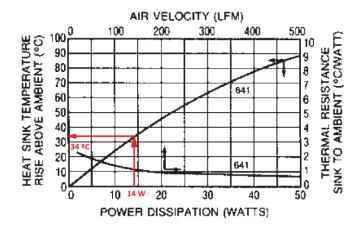

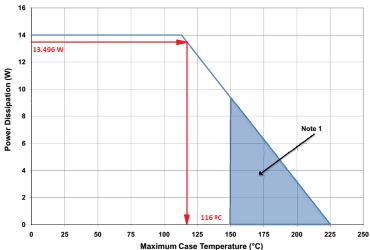

Buscando un disipador en el catálogo de *Wakefield-Vette* encontramos el modelo *641k*. Dicho modelo tiene unas características de convección natural y forzada como las que muestra la Figura 3.1.

Figura 3.1 – Características de convección natural y forzada de nuestro disipador.

Considerando que disipamos alrededor de 14 vatios, tenemos una subida de temperatura sobre la temperatura ambiente de unos 34ºC, aproximadamente. Así pues,

$$\theta_{sa~(641k)} = \frac{34 \, {}^{\circ}C}{14 \, W} \simeq 2.43 \, {}^{\circ}C/W$$

Por lo que el nuevo valor  $heta_{ja}$  sería

$$\theta_{ia~(641k)} = \theta_{ic} + \theta_{cs} + \theta_{sa~(641k)} = 8 + 0.5 + 2.43 = 10.93 \, {}^{\circ}C/W$$

Teniendo el peor caso

$$T_{j\,(641k)} = \theta_{ja\,(641k)} \cdot P_D + T_a = 10.93 \cdot 13.496 + 25 \simeq 172.51\,{}^{\circ}C \ (max.\,225\,{}^{\circ}C)$$

$$T_{c (641k)} = T_{i (641k)} - \theta_{ic} \cdot P_D = 172.51 - 8 \cdot 13.496 \approx 64.54 \, {}^{\circ}C \quad (max. 150 \, {}^{\circ}C)$$

Estos valores corroboran que este disipador trabajará bien incluso en el peor caso.

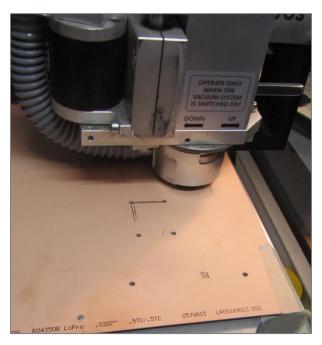

#### 3.2. Conexión a tierra del transistor

La resistencia térmica del pin de la fuente al disipador es el material interfaz empleado para hacer buen contacto térmico entre el transistor y el disipador, en nuestro caso, pasta térmica. Esto significa que el transistor va en contacto directo con el disipador. Hay dos razones que avalan esta configuración:

- Rendimiento térmico. Si no realizamos la muesca en el sustrato, entonces tendríamos que usar el sustrato como material interfaz entre el transistor y el disipador. Esto no es aconsejable porque la resistencia térmica del pin de la fuente al disipador aumentaría demasiado aumentando la posibilidad de quemar el transistor por sobrecalentamiento.

- Reducción de la inductividad asociada a la conexión con tierra. Si optamos por no quitar el sustrato en esa área, deberemos hacer muchos agujeros para evitar que se generen inductancias indeseadas. Es mucho más conveniente quitar esa área de sustrato y "hacer una buena tierra".

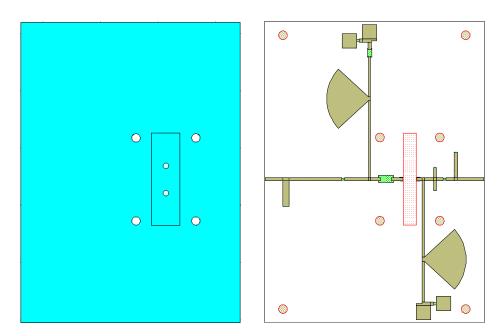

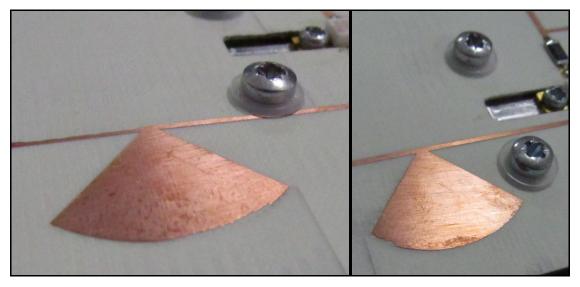

El slot llevado a cabo en el sustrato se puede observar en la Figura 3.2 (derecha) marcado en rojo.

Figura 3.2 – Vista frontal del disipador modificado (izq.) y muesca en el sustrato marcada en rojo (derecha).

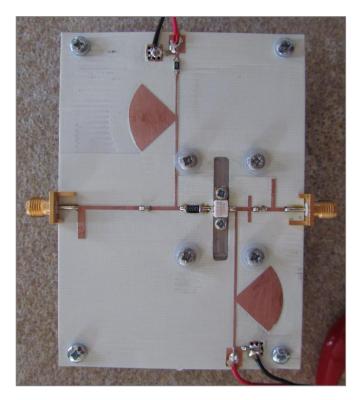

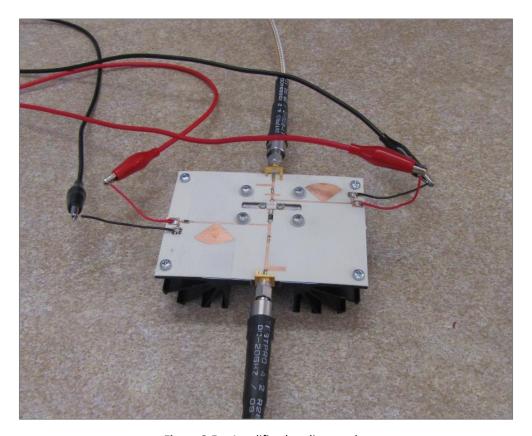

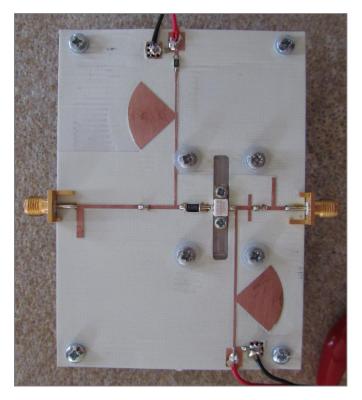

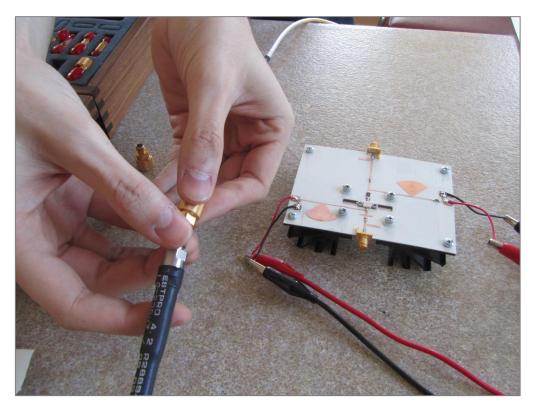

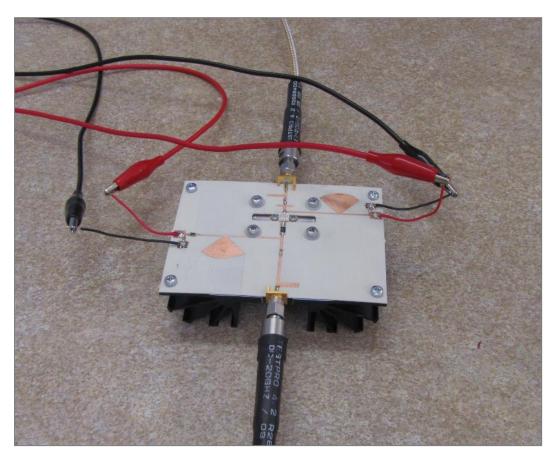

Figura 3.3 – Diseño acabado y listo para el testeo en el laboratorio.

Finalmente montamos el sustrato y el transistor en el disipador junto con todos los componentes. Entre el transistor y el disipador se ha aplicado una fina capa de pasta térmica. El resultado final se puede ver en la Figura 3.3.

#### 3.3. Testeo

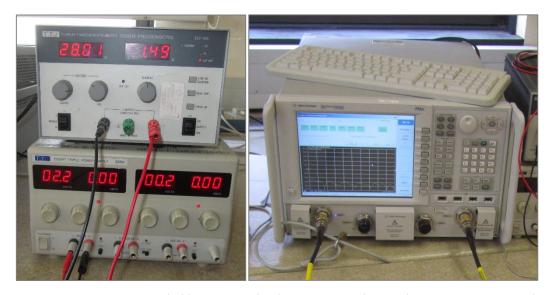

Para la alimentación usamos dos fuentes de corriente continua independientes.

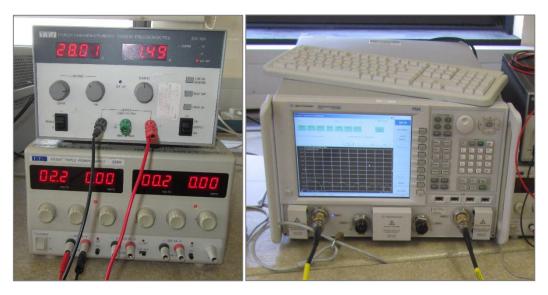

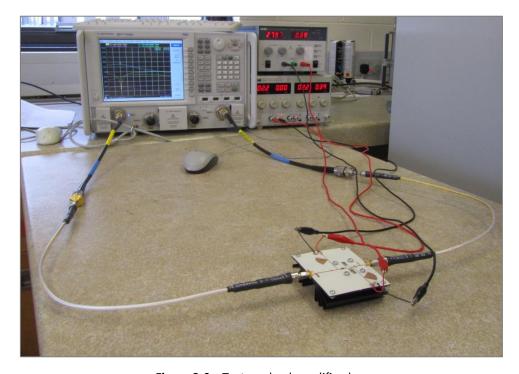

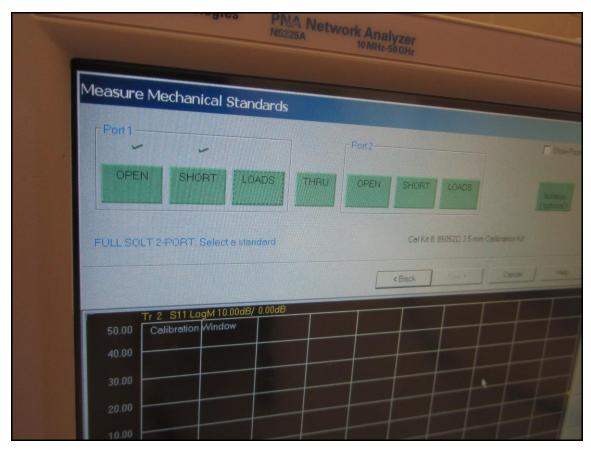

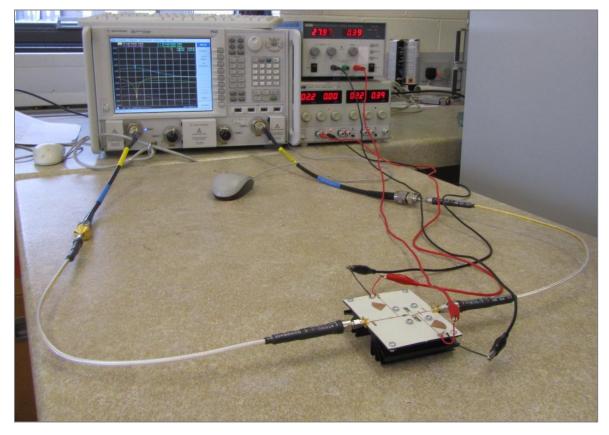

Figura 3.4 – Fuentes de alimentación (izquierda). PNA Agilent N5225A (derecha).

Para el análisis de puertos usamos el PNA (Programmable Network Analyzer) Agilent N5225A.

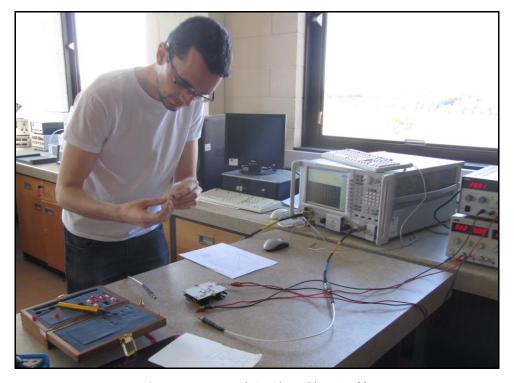

Figura 3.5 – Amplificador alimentado.

Figura 3.6 – Testeando el amplificador.

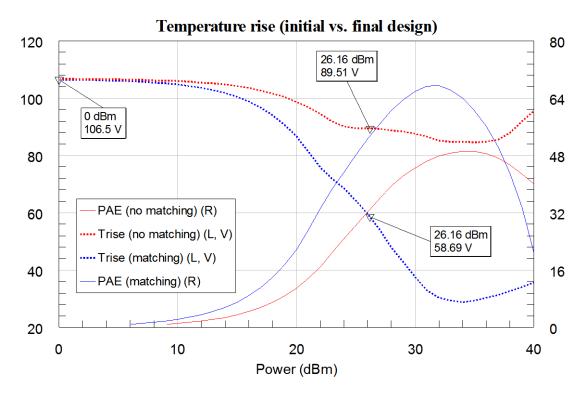

#### 3.4. Resultados

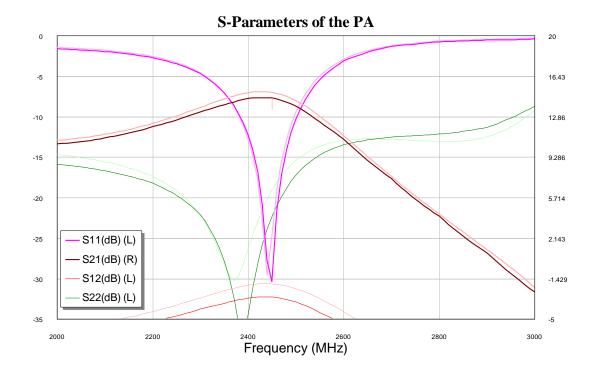

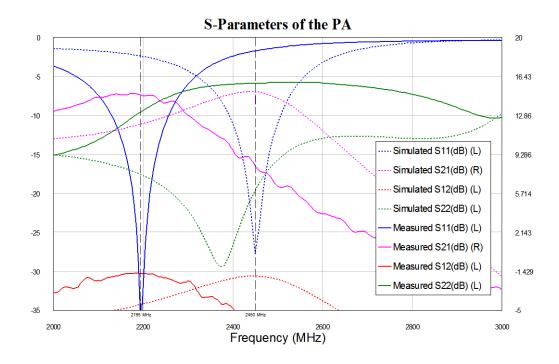

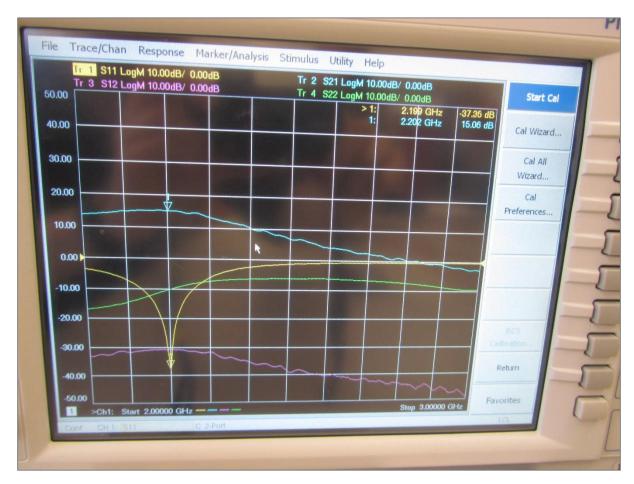

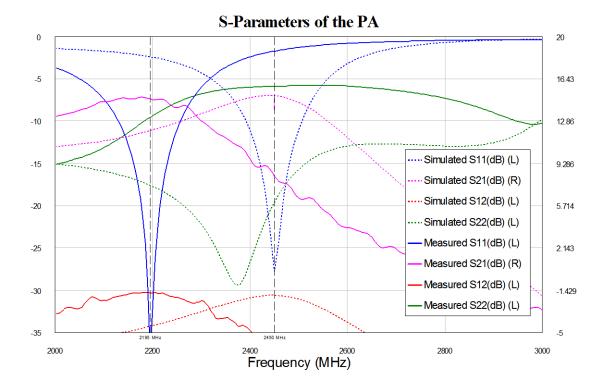

Tal y como podemos observar en la Figura 3.7, los parámetros S son muy similares a los simulados, pero tienen la particularidad de que están desplazados en frecuencia unos 250MHz a la izquierda.

La solución a este problema es relativamente sencilla. La técnica empleada para solucionar esto es la de redimensionar el diseño a una escala que se puede calcular de la siguiente manera,

Resize factor =

$$\frac{f_{shifted}}{f_0} = \frac{2200}{2450} = \frac{44}{49} \approx 0.898$$

Con este factor re-escalamos el tamaño a un diseño más pequeño, y con ello el problema debería desaparecer. El único parámetro que no coincide con los valores simulados es el  $S_{22}$ .

Figura 3.7 – Parámetros S Medidos Vs. Simulados.

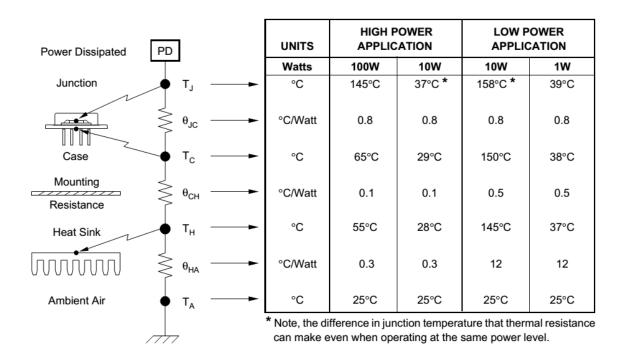

#### 3.5. Problema térmico

Cuando el amplificador se encontraba funcionando aproximadamente unos 4 minutos, los parámetros S comenzaron a desplazarse y desde entonces no volvieron a su posición inicial. Las posibles causas a este problema podrían ser:

- a. La pasta térmica posiblemente no ha sido aplicada de manera correcta. La cantidad puede haber sido insuficiente también.

- b. El punto de reposo elegido (Q-Point) se encuentra casi en el límite de potencia disipada, lo cual hace que el transistor tenga mayores probabilidades de quemarse por sobrecalentamiento.

- c. Las medidas de los parámetros S fueron hechas con una potencia de entrada de 0dBm.

Bajas potencias de entrada desembocan en baja PAE. Y baja PAE significa que la mayor parte de la potencia suministrada al transistor está siendo disipada en calor.

A causa de este problema no fuimos capaces de medir otros parámetros interesantes como la PAE, ganancia, no-linealidades, etc.

#### 3.6. Conclusiones

El análisis, implementación, simulación, fabricación y testeo de un Amplificador de Potencia de clase A en la banda ISM ha sido propuesto. Los resultados iniciales fueron buenos: 15dB de ganancia, P<sub>1dB</sub> a 26dBm aproximadamente y estabilidad incondicional en un amplio rango de frecuencias gracias a las resistencias empleadas.

Los malos resultados del final hacen de este trabajo como una fuente potencial de aprendizaje sobre los problemas surgidos para futuros diseños.

#### 3.7. Líneas futuras

Los principales caminos que se deberían tomar con este trabajo deberían ser:

- 1. Investigar y resolver el problema térmico que hizo sobrecalentar al transistor.

- 2. Hacer más y variadas medidas para comprobar el correcto funcionamiento y para aprender cómo usar el PNA para este propósito.

- 3. Intentar estandarizar el proceso de diseño de un amplificador de potencia y hacerlo más práctico.

- 4. Levar a cabo el diseño de una clase B y AB, entonces seremos capaces de comparar estas tres clases en términos de ruido, no-linealidades, ganancia, eficiencia, etc.

HERIOT-WATT UNIVERSITY - POLYTECHNIC UNIVERSITY OF CARTAGENA

# 2.45GHz Class A GaN HEMT Power Amplifier Design

FINAL DEGREE PROJECT

**Author: Pascual David Hilario Re**

Supervisor: José Luis Gómez Tornero Second supervisor: George Goussetis To my family...

...who made me who I am

To Estela...

...who has supported me so much in difficult times

| Author           | Pascual David Hilario Re                        |

|------------------|-------------------------------------------------|

| Author's email   | pascual.hilario@gmail.com                       |

| Director         | José Luis Gómez Tornero                         |

| Director's email | josel.gomez@upct.es                             |

| Co-director      | George Goussetis                                |

| Title            | 2.45GHz Class A GaN HEMT Power Amplifier Design |

#### **Abstract**

Today, solid state amplification is dominated by use of three-terminal transistors. Using a small voltage applied at the input terminal of the device, one can control, in an efficient manner, a large current at the output terminal when the common terminal is grounded. This is the source for the name transistor, which is a unification of the words transfer resistor.

Thanks to transistors amplification exists and this project is focused in the design process that an engineer must follow in order to create it, from initial simulations in software until testing in the lab.

| Degree          | Telecommunications Engineering             |  |  |  |

|-----------------|--------------------------------------------|--|--|--|

| Department      | Communication and Information Technologies |  |  |  |

| Submission date | October 2015                               |  |  |  |

# **Contents**

| 1. | Intro | oduction                                            | 1  |

|----|-------|-----------------------------------------------------|----|

|    | 1.1.  | Transistor amplifier                                | 2  |

|    | 1.2.  | Early history of transistor amplifiers              | 4  |

|    | 1.3.  | Benefits of transistor amplifiers                   | 5  |

|    | 1.4.  | Applications of amplifiers                          | 5  |

|    | 1.5.  | Current trends                                      | 7  |

|    | 1.6.  | Objectives                                          | 9  |

| 2. | The   | oretical Background                                 | 11 |

|    | 2.1.  | Linear Network Analysis                             | 11 |

|    | 2.:   | 1.1. The concept of Impedance                       | 11 |

|    | 2.:   | 1.2. S-Parameters                                   | 12 |

|    | 2.2.  | Transistors                                         | 14 |

|    | 2.2   | 2.1. BJT                                            | 15 |

|    | 2.2   | 2.2. HBT                                            | 16 |

|    | 2.2   | 2.3. FET                                            | 17 |

|    | 2.2   | 2.4. MOSFET                                         | 18 |

|    | 2.2   | 2.5. LDMOS                                          | 19 |

|    | 2.2   | 2.6. MESFET                                         | 20 |

|    | 2.2   | 2.7. HEMT                                           | 21 |

|    | 2.3.  | Amplifier Characteristics and Definitions           | 23 |

|    | 2.3   | 3.1. Bandwidth                                      | 23 |

|    | 2.3   | 3.2. Power Gain                                     | 23 |

|    | 2.3   | 3.3. Noise Figure                                   | 25 |

|    | 2.3   | 3.4. Output Power and 1-dB Compression Point (P1dB) | 26 |

|    | 2.3   | 3.5. Input and Output VSWR                          | 26 |

|    | 2.3   | 3.6. Power Added Efficiency (PAE)                   | 27 |

|    | 2.3   | 3.7. Intermodulation Distortion                     | 27 |

|    | 2.3   | 3.8. Dynamic Range                                        | 28 |

|----|-------|-----------------------------------------------------------|----|

|    | 2.:   | 3.9. Stability                                            | 28 |

|    | 2.4.  | Amplifier Classes                                         | 29 |

|    | 2.4   | 4.1. Class-A Amplifier                                    | 30 |

|    | 2.4   | 4.2. Class-B Amplifier                                    | 30 |

|    | 2.4   | 4.3. Class-AB Amplifier                                   | 31 |

|    | 2.    | 4.4. Class-C Amplifier                                    | 31 |

|    | 2.    | 4.5. Class-D Amplifier                                    | 31 |

|    | 2.4   | 4.6. Class-E Amplifier                                    | 32 |

|    | 2.4   | 4.7. Class-F Amplifier                                    | 32 |

| 3. | Amp   | olifier Design Method                                     | 33 |

|    | 3.1.  | Stability considerations                                  | 33 |

|    | 3.2.  | Unilateral Approximation                                  | 36 |

|    | 3.3.  | Gain considerations                                       | 37 |

|    | 3.4.  | Design procedures                                         | 39 |

|    | 3.5.  | Selection of the microwave transistor                     | 41 |

|    | 3.6.  | Transistor Characterization                               | 43 |

|    | 3.7.  | Safe Operating Area, Q-Point and Dynamic Load-Line        | 44 |

|    | 3.8.  | Stability analysis                                        | 49 |

|    | 3.9.  | Unilateral Approximation                                  | 52 |

|    | 3.10. | Load-Pull Simulation                                      | 52 |

|    | 3.11. | Biasing networks                                          | 57 |

|    | 3.12. | Real design                                               | 64 |

| 4. | Mar   | ufacturing and Testing Process                            | 73 |

|    | 4.1.  | Heat sink considerations                                  | 73 |

|    | 4.2.  | Transistor grounding and subtractive manufacturing method | 79 |

|    | 4.3.  | Testing                                                   | 83 |

|    | 4.4.  | Results                                                   | 87 |

|    | 4.5.  | Thermal issue                                             | 88 |

| 5. | Con   | clusions and Future Work                                  | 89 |

|    | 5.1.  | Future Work                                               | 89 |

|    | 5.2.  | Personal Feelings                                         | 89 |

| 6. | Refe  | erences                                                   | 91 |

# 1. Introduction

Signal amplification is one of the most important radiofrequency (RF) and

microwave circuit functions. The introduction of radar during World War II provided the first significant application requiring amplification of microwave signals. Nowadays, the wireless communication revolution has provided an explosion of RF and microwave amplification applications. During the last two decades, amplifier technology has made tremendous progress in terms of devices (low noise and power), circuit computer-aided design (CAD) tools, fabrication, packaging, and applications. Low-cost power amplifiers for wireless applications are a testament to this explosion.

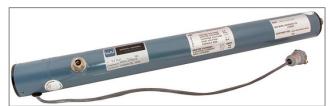

Early microwave amplifiers were the exclusive province of vacuum tube devices such as Klystrons, traveling-wave tube (TWT) amplifiers and magnetrons (Figure 1.1). Today, microwave amplification is dominated by solid state amplifiers except for applications at high output powers (≥100 watts). Today, the most common vacuum tube application is the 900-watt microwave oven using a 2.45GHz magnetron. The power levels achievable for tube amplifiers are on the order of 103 higher than achievable for solid state amplifiers.

Solid state amplifiers are of two general classes: those based on two-terminal negative resistance diode devices, and those based on three-terminal devices known as transistors. Early solid state amplifiers were dominated by two-terminal devices because diodes are typically much easier to fabricate than transistors. Quite an array of two-terminal amplifier designs have been introduced, including parametric amplification (varactor diodes), tunneling diodes, transferred electron diodes (Gunn and LSA diodes) and avalanche transit-time diodes (IMPATT, TRAPATT and BARITT). Such diodes are used only for special amplifier functions. [1]

Figure 1.1 – Klynstron (top-left), TWT (top-right) and magnetron (bottom).

# 1.1. Transistor amplifier

Today, solid state amplification is dominated by use of three-terminal transistors. Using a small voltage applied at the input terminal of the device, one can control, in an efficient manner, a large current at the output terminal when the common terminal is grounded. This is the source for the name transistor, which is a unification of the words *transfer resistor*. Solid state transistors may be grouped into two categories: bipolar and unipolar devices. The bipolar devices are comprised of silicon (Si) bipolar junction transistors (BJTs) and silicon germanium (SiGe) and gallium arsenide (GaAs) heterojunction bipolar transistors (HBTs). The unipolar devices include Si metal oxide semiconductor field effect transistors (MOSFETs), GaAs metal semiconductor field effect transistors (MESFETs), and pseudomorphic high electron mobility transistors (pHEMTs). The switchover to three-terminal devices was largely due to cost. Diodes are typically less expensive to manufacture than transistors but the

associated circuitry to achieve gain from a two-terminal device is much more expensive than that for a three-terminal device. For example, a transistor (without any matching network) connected between 50-ohm input and output terminals can provide 15–20 dB gain at radiofrequencies and 6–8 dB at 20 GHz. In addition, design of three-terminal amplifiers for stable operation and routine high-yield manufacturing is exceedingly simple. Signal amplification is a fundamental function in all RF and microwave systems.

When the strength of a weak signal is increased by a device using a direct current (DC) power supply, the device along with its matching and biasing circuitry is known as an amplifier. Here the DC power from the power supply is converted into RF power to enhance the incoming signal strength. If a device is a transistor, the signal is applied to the input terminal (gate/base) and the amplified signal appears at the output (drain/collector) and the common terminal (source/emitter) is usually grounded. The matching networks help in exciting the device and collecting the output signal more efficiently. Figure 1.2 shows a schematic representation of a single-stage transistor amplifier. Basic constituents are a transistor, input and output matching networks, bias circuitry, and input and output RF connections. The DC bias and RF connections may be made to connectors if housed in a fixture or to lead frame if assembled in a package depending on the amplifier fabrication scheme. [1]

**Figure 1.2** – Transistor amplifier schematic.

The design of amplifiers requires essentially device models/S-parameters, CAD tools, matching and biasing networks, and fabrication technology. RF and microwave amplifiers have the following characteristics:

- Band-limited RF response

- Less than 100% DC to RF conversion efficiency

- Nonlinearity that generates mixing products between multiple signals

- RF coupled and no DC response

- Power-dependent amplitude and phase difference between the output and input

- Temperature-dependent gain, higher gain at lower temperatures and vice versa

# 1.2. Early history of transistor amplifiers

The use of Si based bipolar transistors and GaAs based MESFET for amplifiers have been reported since the mid-1960s and early 1970s, respectively. Most of the initial work on Si based bipolar transistor amplifiers was below C-band frequencies, whereas GaAs based MESFET amplifiers were designed above L-band frequencies. Low-noise HEMTs were reported in the early 1980s. Internally matched narrowband MESFET power amplifiers working from S through X-band were available during the 1980s and Ku-band amplifiers were introduced in the early 1990s.

The GaAs monolithic microwave integrated circuit (MMIC) amplifier was reported in 1976 and since then there has been tremendous progress in both LNAs (Low Noise Amplifiers) and PAs (Power Amplifiers).

Some of the early development milestones in MMIC amplifiers are as follows [1]:

- X-band low-power GaAs MESFET amplifier in 1976

- X-band GaAs MESFET power amplifier in 1979

- K-band GaAs MESFET LNA in 1979

- Q-band GaAs MESFET power amplifier in 1986

- V-band GaAs HEMT LNA in 1988

- X-band GaAs HEMT power amplifier in 1989

- W-band HEMT LNA/power amplifier in 1992

## 1.3. Benefits of Transistor Amplifiers

Major benefits of transistor amplifiers versus tube amplifiers are:

- Smaller size

- Lighter weight

- Higher reliability

- High level of integration capability

- High-volume and high-yield production capability

- Greater design flexibility

- Lower supply voltages

- Reduced maintenance

- Unlimited application diversity

- Have much longer operating life (on the order of millions of hours)

- Require much lower warming time

Solid state amplifiers also do not require adjustment in the bias or the circuit, as required in tubes, over long periods of operation.

In comparison to solid state diode amplifiers, transistor amplifiers have greater flexibility in terms of designing matching networks, realizing high-stability circuits and cascading amplifier stages in series for high gain. The outstanding progress made in monolithic amplifiers is attributed to three-terminal transistors, especially on GaAs substrates. Monolithic amplifiers are fabricated on wafers in batches, and hundreds or thousands can be manufactured at the same time. Thus monolithic amplifiers have a great advantage in terms of the manufacturing cost per unit. It is worth mentioning that the weight of an individual or discrete chip resistor or a chip capacitor or an inductor is typically more than an entire monolithic amplifier chip. Many of today's high-volume applications using amplifiers are in hand-held gadgets. [1]

# 1.4. Applications of amplifiers

In general, a microwave system requires a group of amplifiers. Low-noise amplifiers are integral parts of receivers while transmitters are based on several stages of power amplifiers.

RF/microwave power amplifiers are important circuit components used in every system

including cordless and cellular telephones, base station equipment, spaceborne, airborne, and ground based satellite communications, wireless local area networks, terrestrial broadcast and telecommunications, point-to-point radio (PPR), very small aperture terminal (VSAT) wideband satellite communications, air traffic systems, global positioning system (GPS), phased array radar (PAR), electronic warfare (EW), and smart weapons. Most of these systems require low-cost (high-volume) and more reliable solid state power amplifiers. Cordless and cellular telephones require low-bias operation (2–5 V), single power supply, and very high-efficiency (analog versions) or high-linearity (digital versions) amplifiers. Cellular telephones may also require dual, triple or quad-mode operation including multiple frequencies in both digital and analog versions. Power amplifiers for point-to-point radio and very small aperture terminal applications are operated typically at 8 V. The output power requirements are in the range of 0.2–4 W. On the other hand, for a phased-array antenna (PAA), the amplifiers are typically operated at 10 V and the output power requirements are in the range of 20–40 W per element.

The power level of amplifiers is dictated by the intended application. For example, for cellular base stations and EW, the power levels are in tens to hundreds of watts, while for satellite and radar systems, their levels may be a magnitude higher. For portable wireless handsets and wireless LANs, the required power levels are an order of magnitude lower, usually less than 1 watt. Based on the modulation schemes, the handset requirements can be grouped into two categories: constant envelope and nonconstant envelope. In the former scheme, there is no information contained in the amplitude of the transmitted signal. In this case, the amplifiers are operated in high-efficiency mode. Common applications are groupe special mobile (GSM) and digital European cordless telecommunication (DECT). The latter scheme enhances the spectral efficiency of the signal by incorporating the intended information in the amplitude of the transmitted signal. Most popular applications are code division multiple access (CDMA), wideband code division multiple access (WCDMA), and local area network (LAN). Usually, the amplifiers are operated in linear mode at the cost of amplifier efficiencies. For wireless base stations, high linearity is of paramount importance in power amplifiers. For example, personal communication service (PCS) (1.8-2.0 GHz) requires power levels in the range of 5–200 W.

Figure 1.3 shows an example of a typical microwave amplifier.

Figure 1.3 – Microwave amplifier.

Requirements for power amplifiers vary drastically from one application to another. Usually communication applications require linear operation, while for radar applications high PAE is of prime importance. Personal communication systems working in the 800-MHz to 2.5-GHz range use different digital modulation and access schemes. They require high-efficiency and linear power amplifiers for hand-held as well as for base station applications.

There are several emerging commercial and military applications that require broadband and high-power amplifiers. These include broadband wireless access systems, communication and electronic warfare. [1]

#### 1.5. Current trends

Microwave and millimeter-wave transistor amplifiers have advanced dramatically. Si based CMOS technology circuits operating up to 70 GHz and GaAs/InP based technology operating up to 280 GHz have been realized. The Si LDMOS transistor is a primary power device for base station transmitters up to S-band frequencies. Devices such as pHEMTs and HBTs made on

InP, SiC, and GaN substrate materials have performed beyond 100 GHz. SiC based GaN pHEMT technology has also advanced rapidly and is finding special application where high-power, high-efficiency, low-noise, broadband, and millimeter-wave operation are required. Extremely high-frequency circuits enable a wide range of new applications to be developed in communications, security, medicine, sensing, and imaging. Power amplifiers are vital components in evolving broadband wireless applications including TV broadcasting, voice over Internet protocol (VoIP), video on demand (VOD), online gaming, mobile streaming, and mobile video telephony.

Recently, SiC based transistors operating at 30–50 V have advanced rapidly. SiC MESFETs have increasing applications in high-power wideband at low microwave frequencies and GaN HEMTs on SiC are finding numerous applications where high-power and high-frequency operation is required. Much higher power densities for such devices meet the current need in reducing the cost of solid state power amplifiers. Another emerging technology is GaN HEMT on SiC. This technology has the potential of meeting cost targets for numerous applications, including base station and radar transmitters. These devices are capable of generating hundreds of watts at C/X-band, tens of watts in the millimeter-wave region, and 1–2 W at 100 GHz. Since this technology has an order of magnitude higher breakdown voltage and power density potentials along with an outstanding thermal dissipation substrate, it has all the ingredients required for high-power amplifiers.

The RF and microwave industry is still growing and there is strong evidence that it is being fully supported to meet current trends. New high-volume applications demand low-cost solutions for transmitters based on transistor amplifiers. Current trends are in the areas of improved device models and integrated CAD tools. In a new competitive business environment, it is essential to have accurate device models and suitable circuit design tools to develop state-of-the-art circuits to meet system requirements, including cost and production schedule. It becomes essentially important for amplifier design engineers to develop amplifier products for specific applications on time. For emerging wideband applications that require very high-power (50–200 W) amplifiers with PAE as high as 50%, new circuit topologies to meet these challenging performance goals will be required.

There are continuous trends for improving the performance of LNAs and PAs in order to make them cheaper for high-volume applications. Thus advancements in RFIC and MMIC technologies and packaging will continue with the pace set in the past decade. For highvolume applications, a package (plastic or ceramic) has become an integral part of RFICs and MMICs for power amplifiers. Achieving the smallest size and cheapest product cost requires inexpensive and high-performance leadless surface-mount and ball-grid array packages. Plastic packaging is a preferred technique for small-signal amplifiers and more and more power devices are being housed in plastic packages. Low thermal resistance is another important requirement for such packages. [1]

# 1.6. Objectives

The main objectives and purposes of this final project are:

- Learning the theoretical background about the design of a Power Amplifier.

- Making the design and simulating it through AWR (Microwave Office).

- Manufacturing the final prototype and test it in the lab.

The specifications of our Power Amplifier will be:

- Working at 2.45GHz in a narrowband configuration (100MHz).

- At least 14dB gain at that frequency.

# 2. Theoretical Background

Before that we start explaining the design process of the proposed Power

Amplifier, it is important to make a brief summary of the main theoretical concepts that we will be working with, such as linear network analysis, transistor basics and amplifier characteristics, definitions and classes.

## 2.1. Linear Network Analysis

Linear network analysis methods are the fundamental topics in RF and microwave circuit design. Basically it consists of mathematical relationships between the voltages and currents at various ports of a component, which may be a transistor or a passive element (bond wire, lumped element, microstrip section, coupler, etc.) or an amplifier. Linear characterization is performed at low power levels, hence the origin of "small-signal" network parameters. [2] Microwave network theory was originally developed in the service of radar system and component development at the MIT Radiation Lab in the 1940s. [3]

### 2.1.1. The Concept of Impedance

The term impedance was first used by Oliver Heaviside in the 19<sup>th</sup> century to describe the complex ratio V/I in AC circuits consisting of resistors, inductors and capacitors. This concept was then applied to transmission lines, in terms of lumped-element equivalent circuits and the distributed series impedance and shunt admittance of the line.

We summarize the various types of impedance and their notation:

•  $\eta = \sqrt{\mu/\varepsilon}$  = intrinsic impedance of the medium. This impedance is dependent only on the material parameters of the medium, and is equal to the wave impedance for plane waves.

- $Z_{\omega}=E_{t}/H_{t}=1/Y_{\omega}=$  wave impedance. This impedance is a characteristic of the particular type of wave (TEM, TM and TE).

- $Z_0=1/Y_0=V^+/I^+=$  characteristic impedance. Characteristic impedance is the ratio of voltage to current for a traveling wave on a transmission line. Because voltage and current are uniquely defined for TEM waves, the characteristic impedance of a TEM wave is unique. [3]

#### 2.1.2. S-Parameters

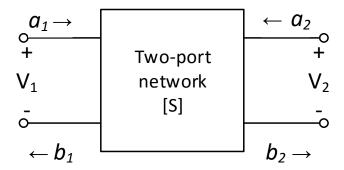

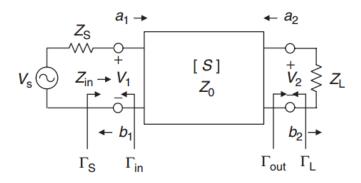

**Figure 2.1** – S-parameter representation of a two-port network.

The scattering matrix formulation is a general method for representing microwave networks and the device under test is usually terminated in  $50\Omega$ . A scattering matrix represents the relationship between variables  $a_n$  (proportional to the incoming wave at the nth port) and variables  $b_n$  (proportional to the outgoing wave at the nth port) defined in the following manner.

$$a_n = \frac{v_n^+}{\sqrt{Z_{0n}}}$$

$$b_n = \frac{v_n^-}{\sqrt{Z_{0n}}}$$

where  $v_n^+$  and  $v_n^-$  represent voltages corresponding to the incoming and the outgoing waves in the transmission line (or the waveguide) connected to the nth port and  $Z_{0n}$  is the characteristic impedance of the line (or waveguide). Knowledge of  $v_n^+$  and  $v_n^-$  is not required to evaluate coefficients of the scattering matrix. Relationships between  $b_n$  and  $a_n$  for the two-port network shown in Figure 2.1 may be written

$$b_1 = S_{11}a_1 + S_{12}a_2$$

$$b_2 = S_{21}a_1 + S_{22}a_2$$

Here

$$S_{11} = b_1/a_1$$

$S_{21} = b_2/a_1$   $a_2 = 0$

$$S_{12} = b_1/a_2$$

$S_{22} = b_2/a_2$   $a_1 = 0$

In general, for an *n*-port network, we have

$$[b] = [S][a]$$

At the *n*th port, the total voltage  $V_n$  and current  $I_n$  are given by

$$V_n = V_n^+ + V_n^- = \sqrt{Z_{0n}}(a_n + b_n)$$

$$I_n = I_n^+ - I_n^- = \frac{V_n^+ - V_n^-}{Z_{0n}} = \frac{1}{\sqrt{Z_{0m}}} (a_n - b_n)$$

Because the current flows in the axial direction, the total (net) current is given by the difference of the currents flowing in the positive and negative directions.

The net average power flow into the network is given by the usual low-frequency relation which is,

$$P_n = \frac{1}{2} Re(V_n \times I_n^*)$$

where  $V_n$  and  $I_n$  denote the total peak voltage and current, respectively. Using the two equations above, we have

$$P_n = \frac{1}{2}(|a_n|^2 - |b_n|^2) + imaginary \ term = \frac{1}{2}(|a_n|^2 - |b_n|^2)$$

This equation shows that the power delivered to a port is equal to the power in the incident wave minus the power in the reflected wave at that port. This is an important term that defines the delivered, incident and reflected powers. The terms  $S_{11}$ ,  $S_{22}$  and  $S_{12}$ ,  $S_{21}$  are defined as the reflection and transmission coefficients, respectively.

Attenuation in a circuit,  $\alpha$ , expressed in dBs, is given by

$$\alpha = -20\log\left|\frac{b_2}{a_1}\right| dB = -20\log|S_{21}| dB$$

For a passive circuit,  $b_2 < a_1$  and value of  $\alpha$  is a positive quantity. However, for an amplifier with gain,  $b_2 > a_1$  and  $\alpha$  becomes a negative quantity. In other words, the negative attenuation is nothing but gain. The transmission phase is given by

$$\phi = \angle S_{21}$$

#### 2.2. Transistors

The realization of high power devices requires an appropriate selection of semiconductor materials and a suitable placing of the emitter/gate fingers to properly balance the heat transfer across the device itself and to avoid peaking junction temperature, thus preventing device failures. Large-scale RF and microwave power device production, especially for commercial purposes, is actually based on silicon (Si), gallium arsenide (GaAs) and related compounds, while great research interest is devoted in the development of high power density devices using wide-bandgap materials such as silicon carbide (SiC) and gallium nitride (GaN). The main substrate properties affecting the device performance, reported in Table 2.1, are represented by the material energy bandgap, the breakdown field, the thermal conductivity, electrons and holes transport properties, the saturated electron velocity and the conductivity which affects the loss behaviour at RF frequencies. [4]

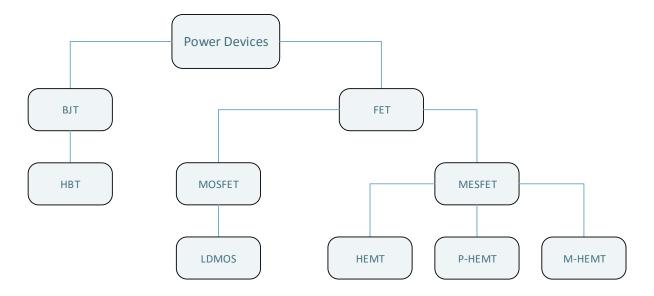

Figure 2.2 – Power transistors classification.

| Property                                                             | Si   | Ge   | GaAs   | GaN    | 4H-SiC | InP    |

|----------------------------------------------------------------------|------|------|--------|--------|--------|--------|

| Electron mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 1500 | 3900 | 8500   | 1000   | 900    | 5400   |

| Hole mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )     | 450  | 1900 | 400    | 350    | 120    | 200    |

| Bandgap (eV)                                                         | 1.12 | 0.66 | 1.42   | 3.2    | 3.23   | 1.35   |

| Avalanche field (10 <sup>5</sup> V/cm)                               | 3.8  | 2.3  | 4.2    | 50     | 35     | 5.0    |

| Saturated drift velocity (10 <sup>7</sup> cm/s)                      | 0.7  | 0.6  | 2.0    | 1.8    | 0.8    | 2.0    |

| Saturation field (10 <sup>3</sup> V/cm)                              | 8    |      | 3      | 15     | 25     | 25     |

| Thermal conductivity at 25°C (W/cm °C)                               | 1.4  | 0.6  | 0.45   | 1.7    | 4.9    | 0.68   |

| Dielectric constant                                                  | 11.9 |      | 12.9   | 14     | 10     | 8      |

| Substrate resistance ( $\Omega$ cm)                                  |      |      | >1000  | >1000  | 1-20   | >1000  |

| Transistors                                                          |      |      | MESFET | MESFET | MESFET | MESFET |

|                                                                      |      |      | HEMT   | HEMT   | HEMT   | HEMT   |

|                                                                      |      |      | HBT    |        |        | HBT    |

|                                                                      |      |      | P-HEMT |        |        | P-HEMT |

**Table 2.1** – Semiconductor properties.

#### 2.2.1. BJT

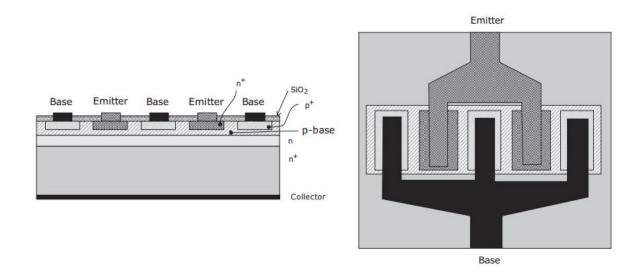

The Bipolar Junction Transistor (BJT) is one of the most essential semiconductor devices, mainly fabricated over silicon in a vertical structure, as schematically depicted in Figure 2.2. The structure is formed by diffusing a p-type region between a heavily doped n+ region and an n-type substrate. The heavily doped n+ region is called the emitter (E), the centre of the p region is called the base (B) and the lightly doped n region is the collector (C).

Figure 2.3 – Schematic structure of a BJT (left) and its top view (right).

Since RF power BJTs are usually realized by composing multiple small BJTs, emitter ballasting is generally employed to force even division of the current within a given package. The Si BJT typically operates from 28 V of bias supply and is adopted up to 5 GHz especially in high power (1 kW) pulsed applications (e.g. radar).

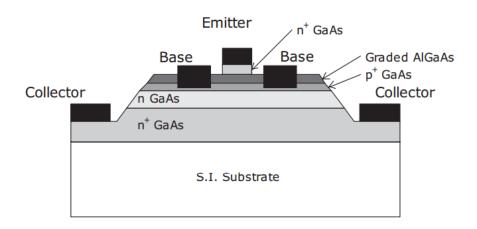

#### 2.2.2. HBT

The Heterojunction Bipolar Transistors (HBTs) represent the natural improvement of conventional BJTs, as a result of the exploitation of heterostructure junctions. Such heterostructures are typically based on compound semiconductor materials like AlGaAs/GaAs, SiGe and InP, as schematically depicted in Figure 2.4 for a GaAs HBT. In order to minimize the base resistance, the emitter is realized as narrow as possible, while the barrier is created directly by the heterojunction (AlGaAs/GaAs in Fig. 2.4) rather than by the doping profile.

**Figure 2.4** – Schematic structure of a HBT.

Unlike conventional BJTs, in HBTs the bandgap difference between the emitter and the base materials results in higher common emitter gain. Base sheet resistance is lower than in ordinary BJTs, and the resulting operating frequency is accordingly higher. The current flow path is vertical, so that surface imperfections affect marginally the device performance. Furthermore, the use of a semiinsulating substrate and the higher electron mobility result in reduced parasitics. GaAs HBT are widely used in MMICs and they operate in PAs at frequencies as high as 20 GHz, while with InP HBT operation up to 50 or 60 GHz has been demonstrated. The main advantage of HBT with respect to FET devices, where PAs are

concerned, is represented by the higher linearity of the former, which seems to be related to the base-emitter junction capacitance and its beneficial effect in reducing the intermodulation products.

#### 2.2.3. FET

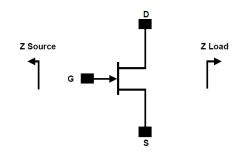

The Field-Effect Transistor (FET) family includes a variety of structures, among which are MESFETs, MOSFETs, HEMTS, LDMOS, etc. They typically consist of a conductive channel accessed by two ohmic contacts, acting as a source (S) and as a drain (D) terminals respectively. The third terminal, the gate (G), forms a rectifying junction with the channel or a MOS structure. A simplified structure of a metal-semiconductor n-type FET is depicted in Figure 2.5.

**Figure 2.5** – Schematic structure of a FET.

Applying a positive voltage Vds between drain and source terminals, electrons flow from the source to the drain, thus creating a current Id in the channel beneath the gate. Thus the source acts as origin of carriers while the drain becomes the sink, and the current flux can be controlled by the rectifying junction formed by the gate terminal and the channel. The gate electrode is deposited to form a Schottky diode in a JFET or MESFET and a metal-oxide (insulator) system in a MOSFET. FET devices ideally do not draw current through the gate terminal, unlike the BJTs which conversely require a significant base current, thus simplifying the biasing arrangement. Moreover, FET devices exhibit a negative temperature coefficient, resulting in a decreasing drain current as the temperature increases. This prevents thermal

runaway and allows multiple FETs to be connected in parallel without ballasting. The device performance is critically determined, over the material properties, by geometrical parameters like the length, width, depth of the channel and depletion layer width. In general, the length of the channel under the gate determines the transit time, i.e. the time required by electrons to travel through the channel itself. This transit time determines the cut-off frequency  $f_T$  and the maximum frequency  $f_{Max}$ . At the same time, however, channel length and inter-electrode spacing (eventually with field-plate arrangements) influence the maximum operating voltage of the transistor, being also determined by the breakdown field of the material.

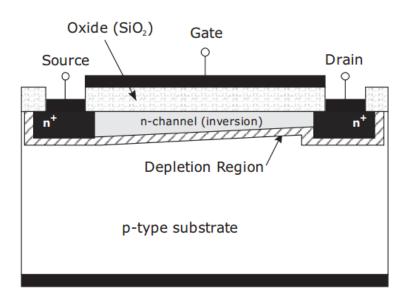

#### 2.2.4. **MOSFET**

The metal—oxide—semiconductor field-effect transistor (MOSFET) is realized by growing an insulated gate above the channel. The latter, according to the doping profile selected, could be already formed (depletion device) or must be created (enhancement device) by suitable gate voltages. As an example, a typical enhancement structure is depicted in Figure 2.6. The standard material used as substrate to grow MOSFET is silicon, whose technology process is sufficiently mature, allowing also the realization of stable oxide used as the dielectric to realize the oxide insulator beneath the gate.

Figure 2.6 – Schematic structure of a MOSFET.

The main issues of MOSFET device are intrinsically related to the oxide insulator, and in particular to the presence of unavoidable traps, which imply a shift in the voltage threshold,

and in the unavoidable parasitics connected with the MOS structure (capacitive in nature) reducing the maximum operating frequency.

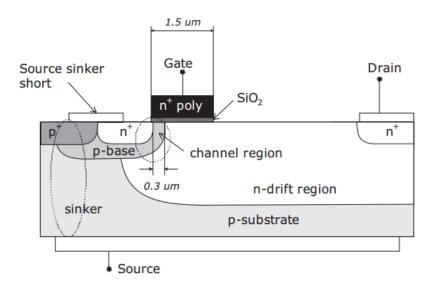

#### 2.2.5. LDMOS

The Laterally Diffused MOSFET (LDMOS) is an enhanced MOSFET structure especially suited for high power applications. Its basic structure is schematically indicated in Figure 2.7. In a LDMOS, as in a MOSFET, there are two n+ regions for the source and the drain respectively. The most noticeable difference as compared to a MOSFET is in the low doped and quite long n-drift region realized in the LDMOS, which enhances the depletion region.

Figure 2.7 – Schematic structure of a LDMOS.

Separating the channel region from the drift region allows designing a short channel device for high frequency operation. At the same time, the increased distance between the drain and source allows higher voltage operation without reaching the breakdown field of the device, thus resulting in higher power capabilities.

The LDMOS drain current follows the same behaviour as in a MOSFET. Applying a positive voltage to the gate, a conductive channel in the p-base region is created. The channel being very short, the device transistor always operates in the saturated velocity region, thus further improving device linearity. Electrons with saturation velocity at the channel flow in the doped n-drift region reaching the drain.

The LDMOS is especially useful at UHF and lower microwave frequencies, since the direct grounding of its source eliminates bond-wire inductance that produces negative feedback and

reduces gain at high frequencies. Currently, packaged LDMOS devices typically operating from 28V supplies and they are available with output powers over 120W at 2GHz.

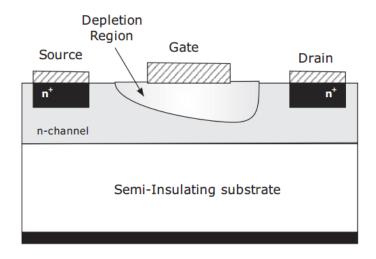

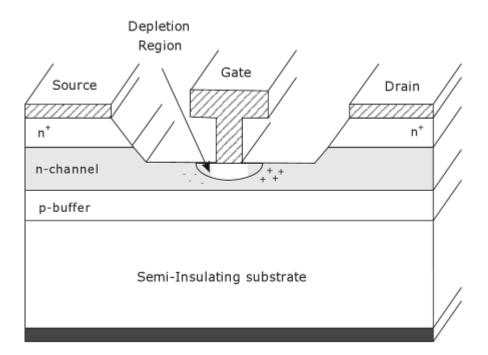

#### 2.2.6. **MESFET**

MEtal-Semiconductor Field-Effect Transistors (MESFETs) have a structure and DC characteristics quite similar to MOSFETs, but differing from the latter since in a MESFET the gate electrode uses a metal semiconductor contact instead of a MOS arrangement. A typical structure of a MESFET is depicted in Figure 2.8. There are two  $n^+$  regions, one for source and the other for the drain, while an n-type channel is present between drain and source terminals and connected to the gate by a Schottky junction. This implies that normally a MESFET device is active for  $V_{gs} = OV$ , thus operating in a depletion-mode requiring negative gate bias, although also enhancement-mode devices that operate with a positive bias have been developed.

Figure 2.8 – MESFET device cross-section.

The source is usually grounded (common source configuration) and the drain is positively biased. Applying a negative gate source voltage reverse biases the metal semiconductor junction, thus forming a depletion layer in the channel. An increase in the negative gate

voltage causes an increase in the depletion region, and a decrease in the conductive channel width: control of the current flow between the drain and source is thus achieved.

MESFET devices are usually fabricated from III-V compound semiconductors; the predominant is GaAs, or more recently from wide-bandgap semiconductors like SiC.

Since III-V compound semiconductors do not allow stable oxide to make the gate dielectric, a Schottky metal semiconductor contact is instead used for the gate. The adoption of Schottky gate results in two main advantages: to avoid traps in the gate insulator, affecting the threshold voltage shift in the MOSFETs, and the absence of the capacitor formed from the channel (conductor), dielectric (insulator) and metal gate terminal (conductor) in normal MOSFET structure, thus allowing higher frequency operation.

Moreover, MESFET based on a GaAs (or SiC) substrate and a Schottky gate junction, exhibit a higher mobility than Si MOSFET devices, thus making them capable of operating with acceptable gain and efficiently at higher frequencies.

The SiC devices, due to their wide energy bandgap and the higher thermal conductivity, provide higher power desities, up to 10W/mm, with respect to the typical values 0.3-0.5W/mm of GaAs based MESFETs.

SiC MESFETs typically operate from 50 to 60 V of DC voltage supply, with some demonstrations extending to hundreds of volts, while GaAs MESFETs are typically operated from supply voltages (drain biases) of 5-10 V.

The higher operating voltage and associated higher load impedance of SiC greatly simplify output networks and power combining. However, the lower carrier mobility in SiC, together with a lower transconductance value, reduces the frequency range of such devices up to 10-12 GHz maximum, against the 25-30 GHz of GaAs MESFETs.

GaAs MESFETs, however, are widely used for the production of microwave power, with capabilities of over hundreds of watts in the L-band or tens of watts up to K-band for packaged devices.

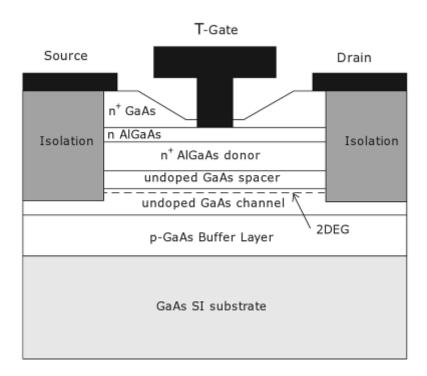

#### 2.2.7. HEMT

In High Electron Mobility Transistors (HEMTs) devices the conducting layers are epitaxially grown over a semi-insulating substrate realizing a heterostructure alongside the electron flow, as schematically depicted in Figure 2.9 for an AlGaAs/GaAs HEMT.

The typical materials used for HEMTs are AlGaAs, Al/InGaAs and AlGaN.

The heterojunction formed results in a sharp dip in the conduction band edge.

Such a discontinuity in the bandgaps of AlGaAs and GaAs causes a thin layer of electrons, i.e. a high carrier concentration in a confined region below the gate at the interface of the AlGaAs and GaAs layers, forming the so-called two-dimensional electron gas (2-DEG). [4]

Figure 2.9 – Structure of an AlGaAs/GaAs HEMT.

It is expected that the high electron mobility transistor (HEMT) using gallium nitride (GaN) as its wide band gap semiconductor will be applied in diverse, green ICT systems because of its high efficiency. The GaN HEMT utilizes high-density two-dimensional electron gas (2DEG) accumulated in the boundary layer between GaN and AlGaN through their piezoelectric effect and natural polarization effect. This makes it possible to realize a low on-state resistance ( $R_{on}$ ). Combined with a high breakdown voltage, the GaN HEMT indicates a superb performance as a power device. After the development of GaN HEMT technology started for power amplifiers of mobile base stations, it was expanded to a radar sensor application. Further expansion of its application is expected in the field of power conversion, in equipment such as server power systems. While the development of GaN HEMT technology has been promoted, focusing on "high output power" conventionally, further advantages such as high efficiency and low energy consumption have been attracting much attention in recent years. [5]

## 2.3. Amplifier Characteristics and Definitions

Although many characteristics must be considered when designing an amplifier, the most important of these are frequency range or bandwidth, power gain, noise figure, power output, 1-dB gain compression point, input and output VSWR, power added efficiency (PAE), intermodulation distortion, dynamic range and stability.

#### 2.3.1. Bandwidth

Generally, the bandwidth of an amplifier is defined as the frequency range over which the circuit meets the specified minimum/maximum or typical aforementioned requirements.

Consider input impedance and output admittance of a transistor as shown in Figure 2.10. In this case input and output 3-dB normalized bandwidths are given by

$$\frac{\Delta f_{in}}{f_0} = \frac{1}{Q_{in}} = 2\pi f_0 R_{in} C_{in} \qquad \frac{\Delta f_{out}}{f_0} = \frac{1}{Q_{out}} = \frac{1}{2\pi f_0 R_o C_o}$$

where  $f_0$  is the centre frequency. This shows that the bandwidth of the transistor is limited by its input impedance, which can be increased by adding more resistance in series with the device. However, it reduces the transistor gain but improves its stability. [6]

Figure 2.10 – One-port equivalent circuit of a transistor: input (left) and output (right).

#### 2.3.2. Power Gain

The power gain of a two-port network, amplifier in this case, is defined as the ratio of the output power to input power. For a two-port network (shown in Figure 2.11), the power gain can be defined in several ways. The three commonly used definitions are *transducer power*

gain  $(G_T)$  or simply power gain, maximum available power gain  $(G_A)$ , and available power gain  $(G_P)$ . Their definitions are given below:

$$G_T = \frac{power\ delivered\ to\ the\ load}{power\ available\ from\ the\ source} = \frac{P_L}{P_{avs}}$$

$$G_A = \frac{power\ available\ from\ the\ network}{power\ available\ from\ the\ source} = \frac{P_N}{P_{avs}}$$

$$G_P = rac{power\ delivered\ to\ the\ load}{power\ delivered\ to\ the\ network} = rac{P_L}{P_{in}}$$

Here  $G_A \ge G_T$  and  $G_P \ge G_T$ .

Developing the power expressions, we have

$$P_{L} = \frac{|V_{S}|^{2}}{8Z_{0}} \frac{|S_{21}|^{2} (1 - |\Gamma_{L}|^{2})|1 - \Gamma_{S}|^{2}}{|1 - S_{22}\Gamma_{L}|^{2}|1 - \Gamma_{S}\Gamma_{in}|^{2}}$$

$$P_{avs} = \frac{|V_{S}|^{2}}{8Z_{0}} \frac{|1 - \Gamma_{S}|^{2}}{1 - |\Gamma_{S}|^{2}}$$

$$P_N = \frac{|V_S|^2}{8Z_0} \frac{|S_{21}|^2 (1 - |\Gamma_{out}|^2)|1 - \Gamma_S|^2}{|1 - S_{22}\Gamma_{out}^*|^2 |1 - \Gamma_S\Gamma_{in}|^2}$$

$$P_{in} = \frac{|V_S|^2}{8Z_0} \frac{|1 - \Gamma_S|^2 (1 - |\Gamma_{in}|^2)}{|1 - \Gamma_S \Gamma_{in}|^2}$$

And substituting these expressions in the gain equations we have

$$G_T = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|(1 - S_{11}\Gamma_S)(1 - S_{22}\Gamma_L) - S_{12}S_{21}\Gamma_S\Gamma_L|^2}$$

If our amplifier can be considered as unilateral ( $|S_{12}| = 0$ ), our transducer power gain becomes in unilateral transducer power gain and it is expressed by

$$G_{TU} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|(1 - S_{11}\Gamma_S) (1 - S_{22}\Gamma_L)|^2} = G_S |S_{21}|^2 G_L$$

where

$$G_S = \frac{1 - |\Gamma_S|^2}{|1 - S_{11} \Gamma_S|^2}$$

$G_L = \frac{1 - |\Gamma_L|^2}{|1 - S_{22} \Gamma_L|^2}$

The terms  $G_S$  and  $G_L$  represent the gain or loss of the input and output matching circuits, respectively.

Figure 2.11 – Two-port network for a transistor.

The maximum unilateral power gain is attained when  $\Gamma_S = S_{11}^*$  and  $\Gamma_L = S_{22}^*$ , that is, when the network is matched conjugately at the input and output ports. The maximum unilateral power gain, also called the maximum available gain from a unilateral device, is given by

$$G_A = G_{TUm} = \frac{|S_{21}|^2}{(1 - |S_{11}|^2)(1 - |S_{22}|^2)}$$

Thus the maximum available gain is the product of the transistor transducer power gain  $|S_{21}|^2$  between source and load impedances (usually 50  $\Omega$ ) and the increase in gain due to matching the input port  $(1 - |S_{11}|^2)^{-1}$  and matching the output port  $(1 - |S_{22}|^2)^{-1}$ . In other words, a single-stage amplifier design consists of (a) designing an input matching network to give  $\Gamma_S \approx 0$  and (b) designing an output matching network that simultaneously gives  $\Gamma_L \approx 0$ . The above conditions fail if the solid state devices are unstable. [6]

The most commonly used gain definition in amplifiers is *transducer power gain*,  $G_{\tau}$ ; other gain definitions are normally used to characterize a transistor. The power gain G is usually expressed in decibels, that is,

$$G(dB) = 10 \log G$$

(power ratio)

#### 2.3.3. Noise Figure

The noise figure of any linear two-port network can be defined as

$$F = \frac{signal \ to \ noise \ ratio \ @ \ input}{signal \ to \ noise \ ratio \ @ \ output} = \frac{available \ noise \ power \ @ \ output}{gain \times available \ noise \ power \ @ \ input} = \frac{N_0}{GkTB}$$

where  $N_0$  is the available noise power at output, G is the available gain of the network over the bandwidth B, and T is the operating temperature in kelvin units.

If  $N_a$  is the noise power added by the amplifier, then

$$F = \frac{GkTB + N_a}{GkTB} = 1 + \frac{N_a}{GkTB}$$

An amplifier that contributes no noise to the circuit has F = 1. [6]

#### 2.3.4. Output Power and 1-dB Compression Point ( $P_{1dB}$ )

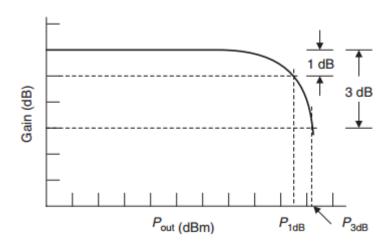

Power delivered to the load ( $P_L$ ) is known as the output power,  $P_o$  or  $P_{out}$ , which is a strong function of the input power. When the gain is reduced at higher input power levels (as the device gets saturated or compressed) by 1 dB, the output power is defined as  $P_{1dB}$ , which is normally used to characterize nonlinearity in amplifiers. At 3–5dB gain compression, the output power is saturated and known as  $P_{sat}$ . Figure 2.12 shows a typical variation of gain with output power of an amplifier. Output power points at 1 and 3dB gain compression are also shown. [6]

Figure 2.12 – Gain versus output power of an amplifier.

#### 2.3.5. Input and Output VSWR

The input and output VSWR values are commonly used to characterize an amplifier's circuit match to source and load impedance (usually  $50\Omega$ ). Mismatch between  $50\Omega$  and the

amplifier's input, and  $50\Omega$  and the amplifier's output are measured as input and output reflection coefficients. When the voltage reflection coefficient  $|\rho| = 0.333$  (VSWR = 2), the power reflection coefficient  $|\rho|^2 = 0.11$  means 11% power is reflected. In most applications, a VSWR value of 2:1 is acceptable.

The reflection coefficients are measured at small-signal conditions as well as at large-signal conditions. The measurement of output reflection coefficient under high-power conditions is not trivial. The output of power amplifier circuits is designed to provide optimum power performance, not necessarily good VSWR.

Normally, good input and output VSWR values in power amplifiers are achieved by using a balanced configuration or by using a traveling-wave combining technique. [6]

Three related parameters—the return loss ( $R_L$ ), VSWR, and reflection coefficient ( $\rho$ )—are commonly used to characterize amplifier reflections. The return loss is the ratio of the input power ( $P_{in}$ ) to reflected power ( $P_R$ ):

$$R_L = -10 \log \frac{P_R}{P_{in}} = -10 \log \left( \frac{VSWR - 1}{VSWR + 1} \right)^2 = -10 \log(|\rho|^2)$$

#### 2.3.6. Power Added Efficiency (PAE)

Power-Added Efficiency (PAE) is a measure of the power conversion efficiency of power amplifiers. Ideally, all supplied power to the amplifier is converted into output power. However, that is not the case in reality. As such, PAE is an important performance parameter for power amplifiers, and is commonly defined as

$$PAE(\%) = \frac{P_{RFout} - P_{RFin}}{P_{DC}} \cdot 100$$

Between linear and saturation regions of operation, there is a point where the power amplifier is most efficient. Up to a certain point, output power is improved while input power is increased. Beyond that point, increased input power will only generate more heat for the device. The objective of PAE measurement is to find this optimal point, the point where the power amplifier is most efficient in transferring input power into output power. [7]

#### 2.3.7. Intermodulation Distortion

An amplifier is called linear when the output power increases linearly with the input power or power gain is constant with input power. As input power increases, the device current

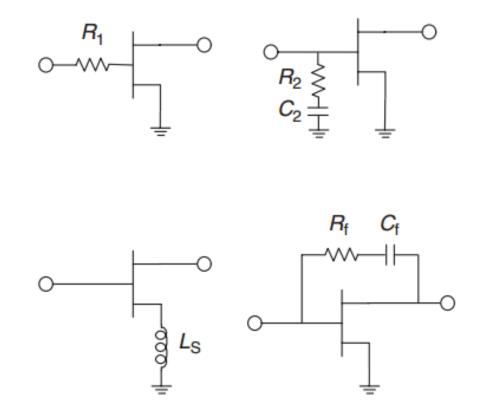

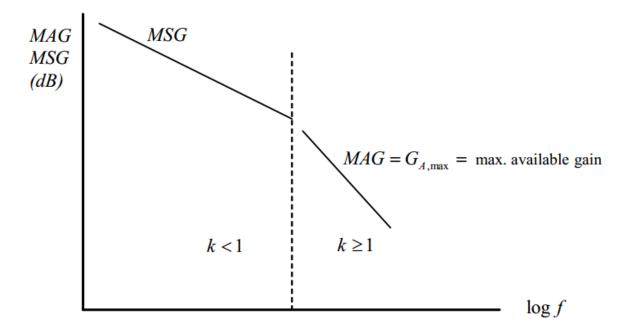

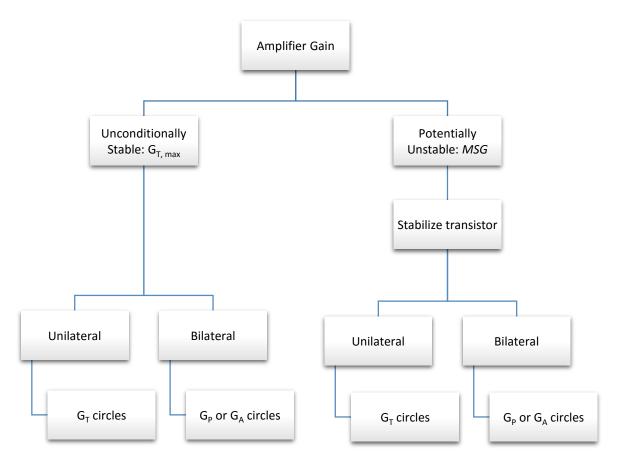

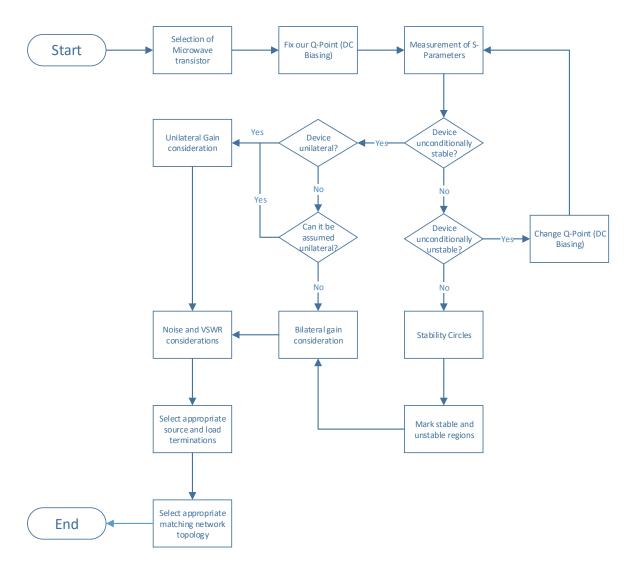

starts reaching its maximum value depending on its size. Near the limiting region the amplifier transfer function becomes nonlinear and a point is reached where the output power does not increase with the input power. One of the measures of nonlinearity of amplifiers is intermodulation distortion. When more than one carrier frequency is present in a nonlinear amplifier, due to mixing, multiple sidebands will be generated as intermodulation products. Intermodulation distortion can also arise from the combined effects of amplitude modulation (AM) introduced by a previous stage and AM to PM (phase modulation) conversion. Intermodulation distortion can be introduced by any nonlinear devices or amplifier stage.